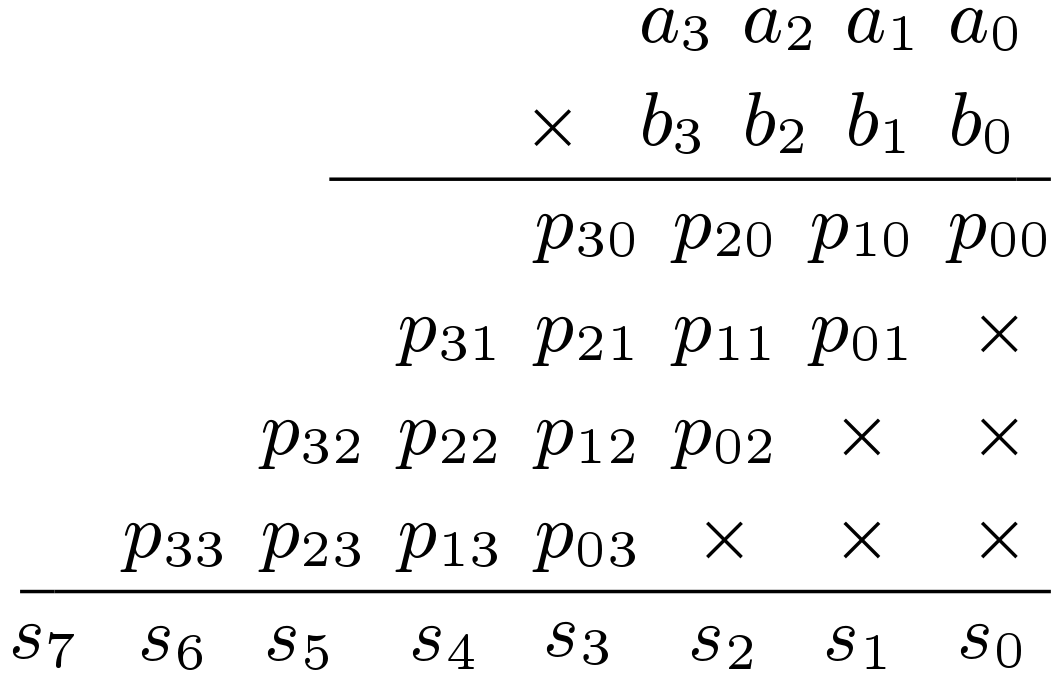

Sequential Multiplier is an old method to multiply two binary numbers. But it is also relevant in many architectures and it is the base of many newly developed multiplication techniques. The multiplication between a and b is shown below.

The multiplication between two operands a and b can be considered as add the operand a total b times. For example, s = 5 X 3 = 5 + 5 + 5 = 15. Serially 5 is added total 3 times to compute the final result. Thus total one adder is sufficient. For a word length of 4-bits, width of the multiplication result is 8-bit. So, an 8-bit adder is required.

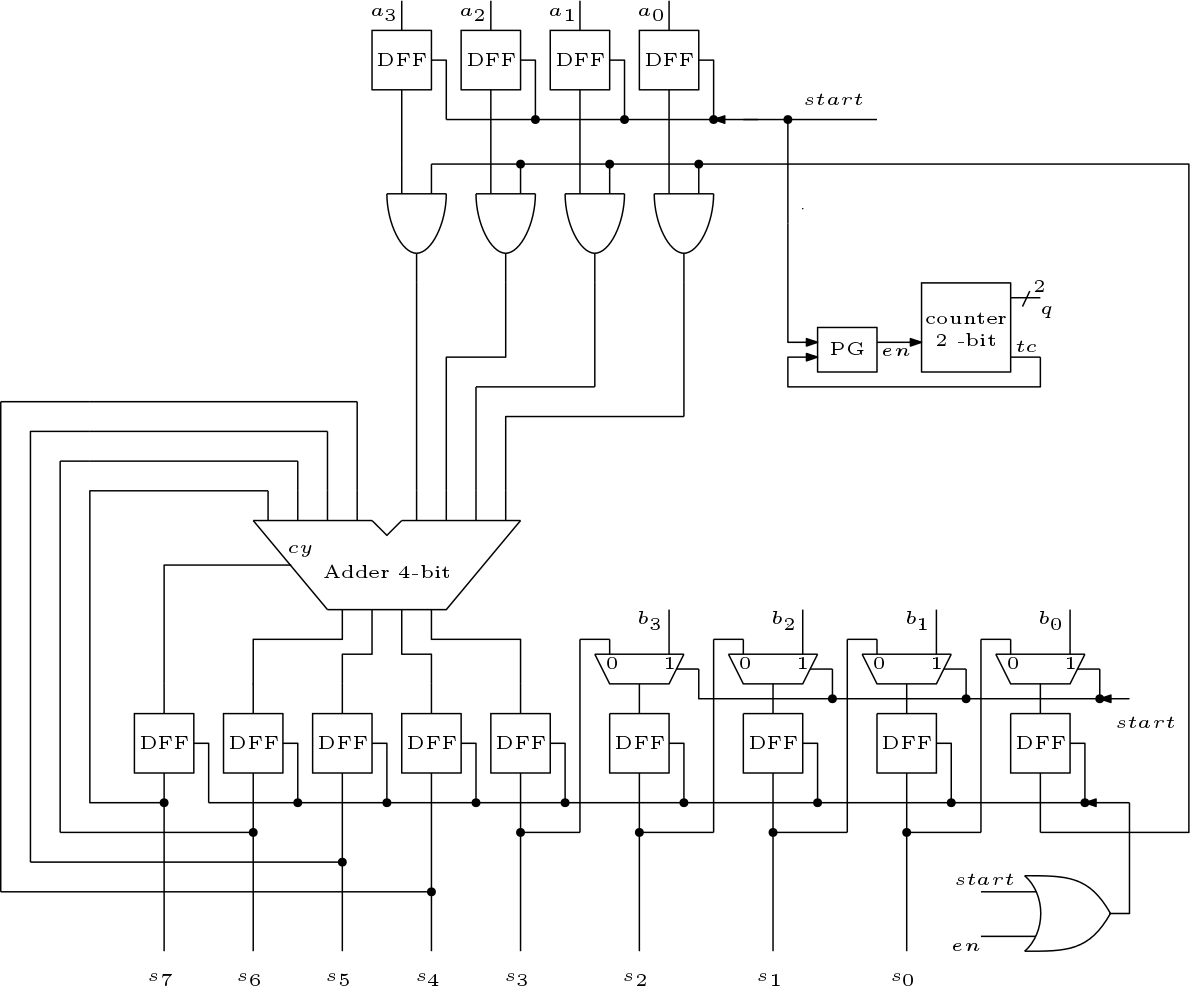

An alternative method is shift and add method. If any bit in the multiplier (b) is 0 then the multiplicand (a) is added with zero. An adder is used which is of the same length as of the operands. Output of the adder and the multiplier is augmented in a register bank. After each addition contents of the register bank is shifted right. A scheme of serial addition is shown below.

The start signal starts the multiplication process. It loads the multiplicand (a) in a register and also loads the multiplier (b) in another register. Each D flip flop is controlled by a control signal. The DFFs shifts data to the right only when the control signal is high. The counter tracks the latency of the multiplier. The PG block is there to generate the enable signal for the counter and the bottom register. The start pulse generates the en signal.

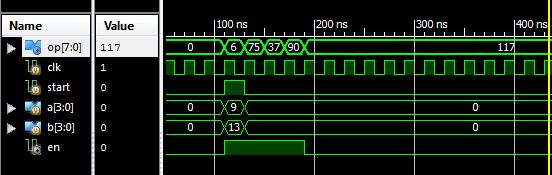

The simulation of the serial multiplier is shown below.

Click here to download the Verilog code

I need the verilog code of an 8bit sequential mutiplier in structural type.

I think i have provided a code for the sequential multiplier in structural style. You can make it for your requirement.

Okay..Thanks a lot.

Yes Sir, I got the code but it is showing some error.

“seq_mul_tb.v:35: error: Unknown module type: seq_mul

2 error(s) during elaboration.

*** These modules were missing:

seq_mul referenced 1 times.”

Could you please help me with this?

you have to add all the verilog files and then only u can simulate the top module seq_mul….

Hii Sir is it working code because i am not getting result of multiplication can you write more steps how to run it

The code is working…You can mention the errors u r getting while running it….

can you elaborate on how to run this code? Cause I am getting the same error

can u specify what error u r getting?

Hi sir,

Can i get the verilog code for vedic multiplier in sequential mode?

I have not written code for Vedic Serial multiplier but you can write it and submit here.

I have downloaded the codes sir, but i don’t know how to execute them.

Can you please share the iverilog/vvp/gtkwave commands to execute it?

I have run the code and got it to work though I have a few doubts. My first doubt is what are the intermediate numbers that are found in between for example 6, 75,37,90(I understand the method is shifting and later adding but I still am not understanding what the intermediate numbers are) that are seen and also when I try adding my own numbers later in the test bench the output gets completely messed up… Any idea why? Thank you so much!!

Sir in the output op[7:0] ,represent what?

The 6, 75,37,90?

op[7:0] means 8-bit part of the vector op.