Latest Posts

LED and Camera Interfacing with ZYNQ FPGA using PYNQ

Python productivity on Zynq (PYNQ) open-source software framework has paved the way for easy implementation of digital systems on Xilinx system on chip (SoC) devices. This project focuses on image acquisition problem in real-time image processing systems. Nowadays it is …

FPGA Implementation of Taylor Series Based Exponential

Exponential function is very important to evaluate activation functions (Sigmoid, hyperbolic tangent, SoftMax etc.) used in machine learning (ML) algorithms. Thus, efficient hardware implementation of exponential function very important. In this post, we have discussed detailed FPGA Implementation of Taylor …

Basic Combinational Blocks using Vivado HLS

Vivado HLS is designed for high level language synthesis of digital systems. Any system can be modelled using lower-level languages like Verilog HDL, VHDL. But these HDL languages are considered as machine level languages like assembly language in case of …

General Verilog Codes for Sequential Blocks

In our previous post, we discussed about general codes for some of the most important combinational blocks. In this post, we will discuss general Verilog codes for some of the most important sequential blocks. General Verilog Codes for Sequential Blocks …

General Verilog Codes for Combinational Blocks

In our previous blog, we discussed different combinational circuits but General Verilog codes are essential in writing bigger complex codes for a system. They make it easy for the coders to generalize the overall code. The generalized overall code can …

Double Flip-Flop Synchronizer for CDC

As we discussed in the previous blog one of the methods to solve metastability is the Double Flop Synchroniser method. This method consists of two cascaded D flip-flops that sample the input signal with the destination clock. This design can …

Clock Domain Crossing in Digital Circuits

Clock Domain Crossing (CDC) refers to the process and techniques used to manage data transfer between different clock domains within the digital system in either ASIC IC or FPGA. CDC is one where the data is transferred from one clock …

FPGA Implementation of XOR Function using ANN

Artificial Neural Networks (ANN) are very popular to realize different critical functions related to any field of study. In this project, a simple exclusive-OR function is realized with the help of ANN. The purpose of the XOR function is to …

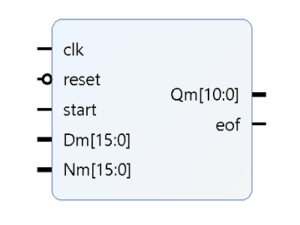

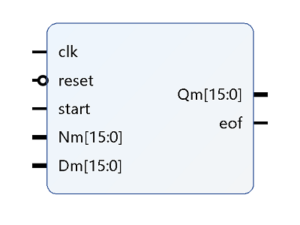

Solving Linear Equations using QR Decomposition

QR decomposition is another powerful technique to solve linear equations. In QR decomposition, the co-efficient matrix $A \in \mathcal{R}^{M\times K}$ need not to be a symmetric matrix. In special cases where the input signal is compressible or sparse, QR decomposition …

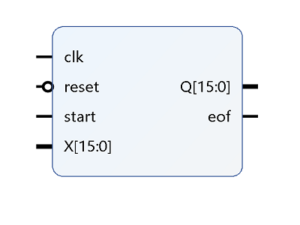

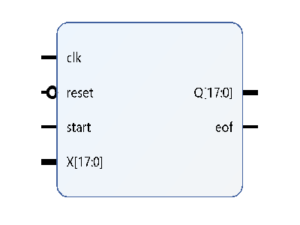

Solving Linear Equations using Gaussian Elimination

Gaussian Elimination (GE) is one of the most popular methods to solve an linear equation. GE algorithm is the only direct method which is of much interest to the researchers. This method considers that the co-efficient matrix is square. If …

Solving Linear Equations with Modified Cholesky Decomposition

In our previous tutorial, we have discussed about Cholesky decomposition which is a very important matrix factorization to solve a linear equation. But this technique has some drawbacks which are also discussed in the same tutorial. In this tutorial, we …

Solving Linear Equations using Cholesky Decomposition

Cholesky decomposition is a very important matrix factorization technique which is used to solve a linear equation. This technique originally derives from very popular LU decomposition and very suitable for higher order matrices. In Cholesky decomposition, the co-efficient matrix $A$ …

Recent Products

-

Verilog Code for Matrix Inversion for Triangular Matrices$10.00

Verilog Code for Matrix Inversion for Triangular Matrices$10.00 -

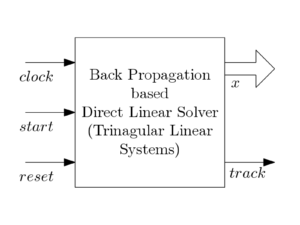

Verilog Code for Back Propagation to Solve Triangular Linear System$10.00

Verilog Code for Back Propagation to Solve Triangular Linear System$10.00 -

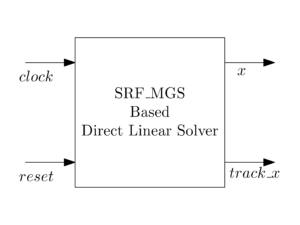

Verilog Code for Direct Linear Solver by Modified Gram Schimdt (MGS) Technique$15.00

Verilog Code for Direct Linear Solver by Modified Gram Schimdt (MGS) Technique$15.00 -

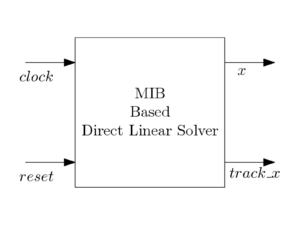

Verilog Code for Direct Linear Solver by Matrix Inversion Bypass (MIB) Technique$15.00

Verilog Code for Direct Linear Solver by Matrix Inversion Bypass (MIB) Technique$15.00 -

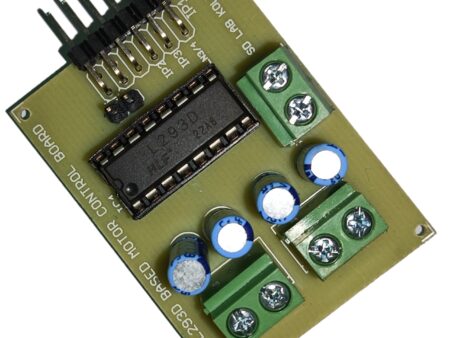

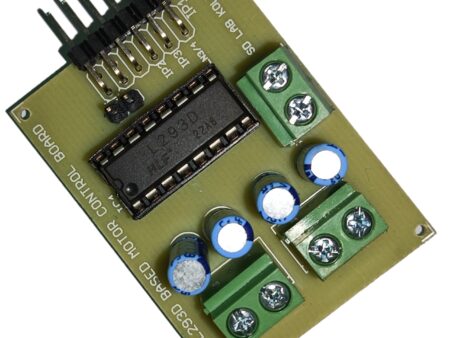

L293D IC Based Motor Driver Module$3.00

L293D IC Based Motor Driver Module$3.00 -

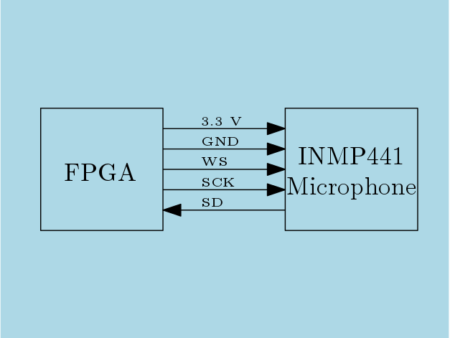

Verilog Code for Interfacing INMP441 MEMS Based Microphone Module$5.00Rated 4.00 out of 5 based on 1 customer rating

Verilog Code for Interfacing INMP441 MEMS Based Microphone Module$5.00Rated 4.00 out of 5 based on 1 customer rating -

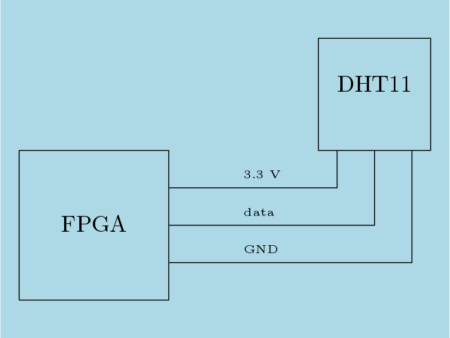

Verilog Code for Interfacing DHT11 with FPGA$10.00Rated 5.00 out of 5 based on 1 customer rating

Verilog Code for Interfacing DHT11 with FPGA$10.00Rated 5.00 out of 5 based on 1 customer rating -

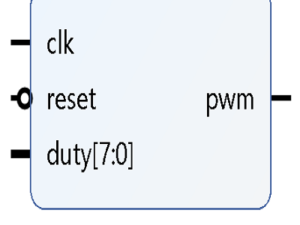

Pulse Width Modulation (PWM) Signal Generator IP$2.00

Pulse Width Modulation (PWM) Signal Generator IP$2.00

Arithmetic Blocks

-

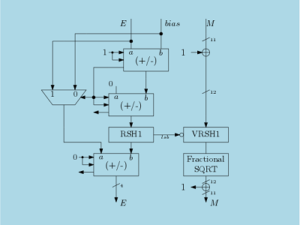

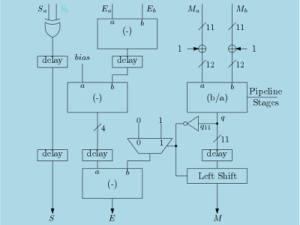

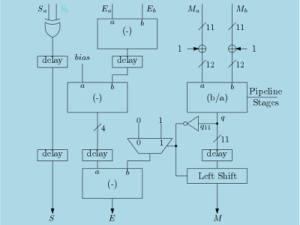

Floating Point General Divider IP$5.00

Floating Point General Divider IP$5.00 -

Fixed Point Reciprocal Computation IP$5.00

Fixed Point Reciprocal Computation IP$5.00 -

Fixed Point Signed Divider IP$5.00

Fixed Point Signed Divider IP$5.00 -

Floating Point Square Root IP$5.00

Floating Point Square Root IP$5.00 -

Fixed Point Square Root IP$5.00

Fixed Point Square Root IP$5.00 -

Verilog Code for 11-bit Floating Point Parallel Square Root Block$2.50Rated 5.00 out of 5 based on 1 customer rating

Verilog Code for 11-bit Floating Point Parallel Square Root Block$2.50Rated 5.00 out of 5 based on 1 customer rating -

Verilog Code for 16-bit Floating Point Pipelined Divider$4.00

Verilog Code for 16-bit Floating Point Pipelined Divider$4.00 -

Verilog Codes for Floating Point Arithmetic Blocks$6.00Rated 2.00 out of 5 based on 1 customer rating

Verilog Codes for Floating Point Arithmetic Blocks$6.00Rated 2.00 out of 5 based on 1 customer rating

Physical Products

-

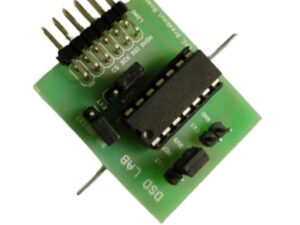

L293D IC Based Motor Driver Module$3.00

L293D IC Based Motor Driver Module$3.00 -

Common Cathode 2-digit Seven Segment Display Module$3.00

Common Cathode 2-digit Seven Segment Display Module$3.00 -

DAC Breakout Board for MCP4922$9.00Rated 5.00 out of 5 based on 1 customer rating

DAC Breakout Board for MCP4922$9.00Rated 5.00 out of 5 based on 1 customer rating -

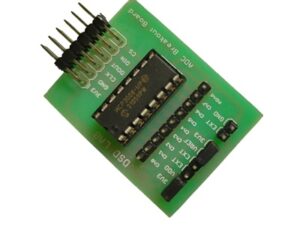

ADC Breakout Board for MCP3008$10.00Rated 5.00 out of 5 based on 1 customer rating

ADC Breakout Board for MCP3008$10.00Rated 5.00 out of 5 based on 1 customer rating