This tutorial is on functional simulation of digital circuits on Genus tool of CADENCE software for ASIC Implementation.

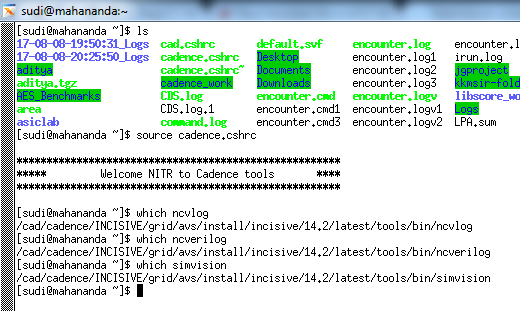

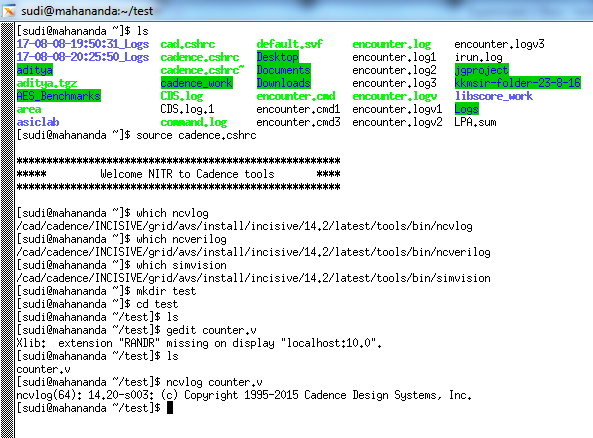

- Open the terminal

- Source the cadence.cshrc

- Check whether the commands are working as below: –

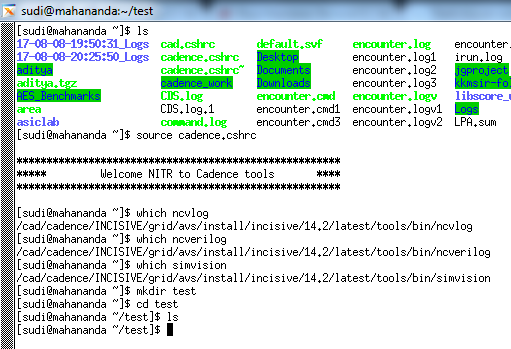

- Create a directory for saving files as below

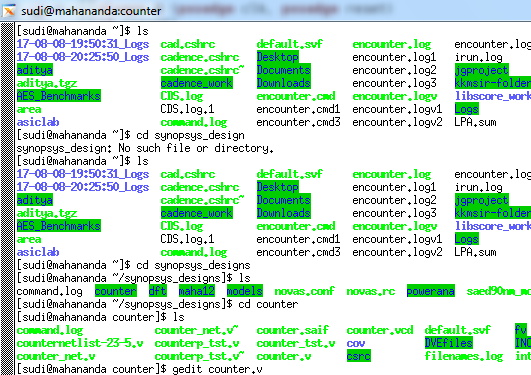

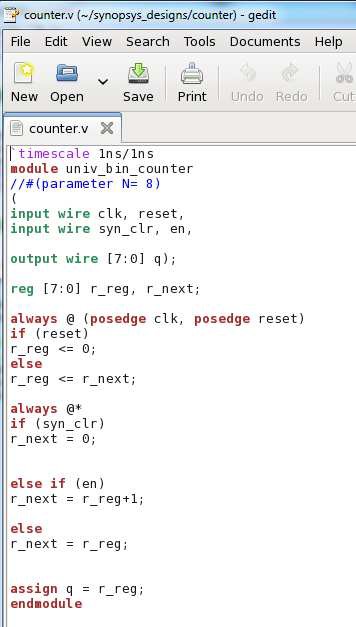

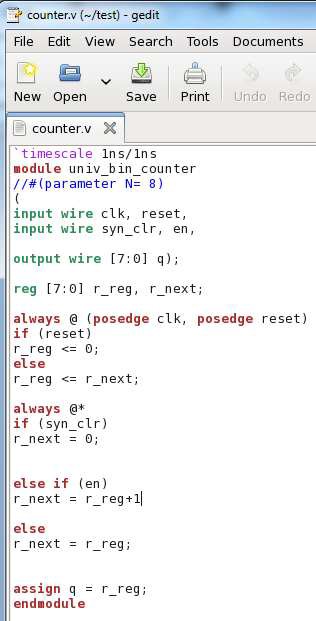

- Create design_file.v as shown below: – (gedit counter.v)

- Check the syntax of design.v (in this example: counter.v) (no syntax errors found)

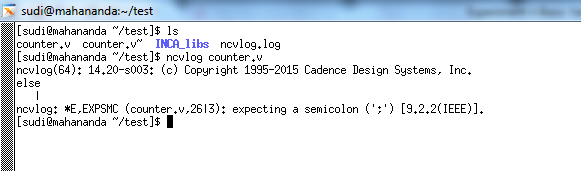

- Induce syntax error in line 24 by removing semicolon

- Perform syntax check: – (shows syntax near 26|3)

- Correct the syntax check and save the file.

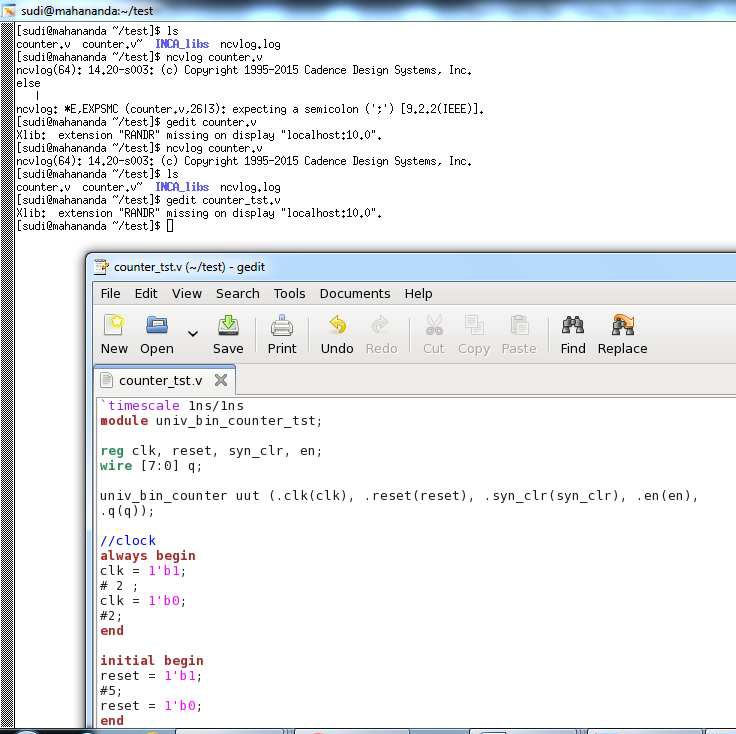

- Similarly create the testbench file for design, check syntax and save the file. (Shown below)

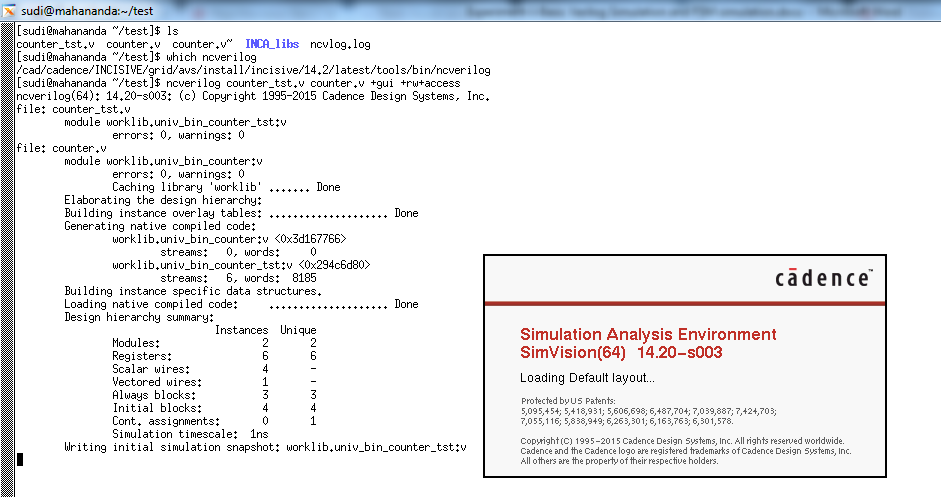

- Execute the command as below: – ncverilog counter_tst.v counter.v +gui +rw+access

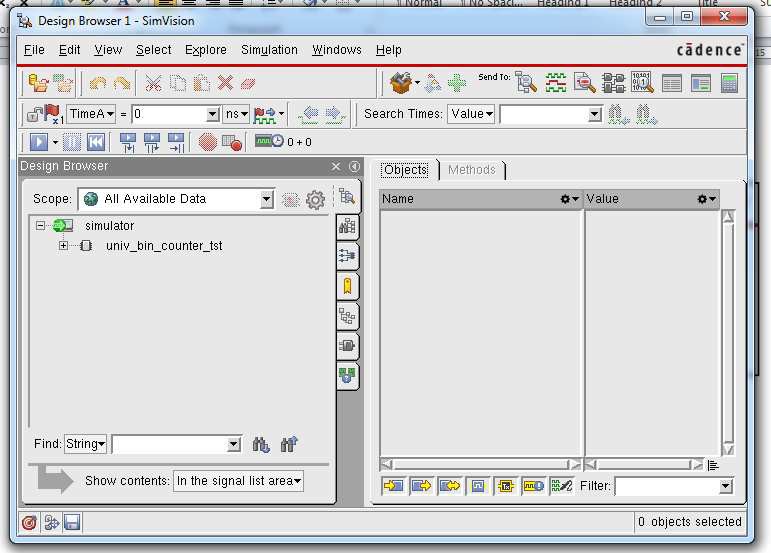

- Simvision gui will open: –

- Simvision gui will open: –

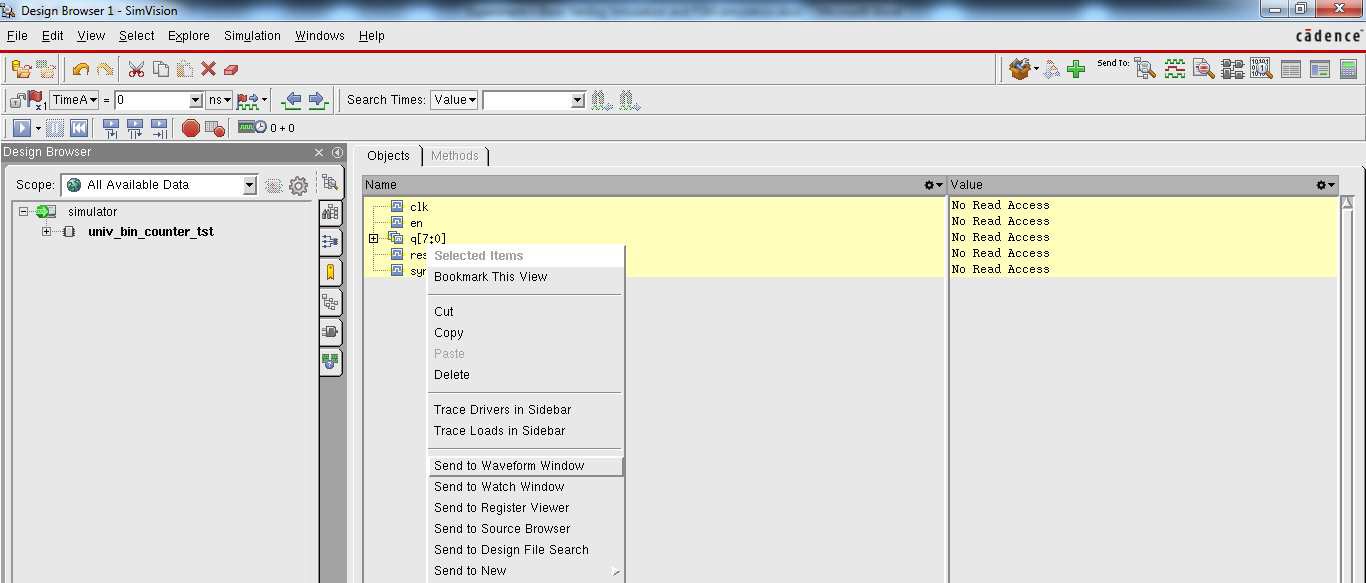

- Right click on signals as shown below and send to Waveform Window:

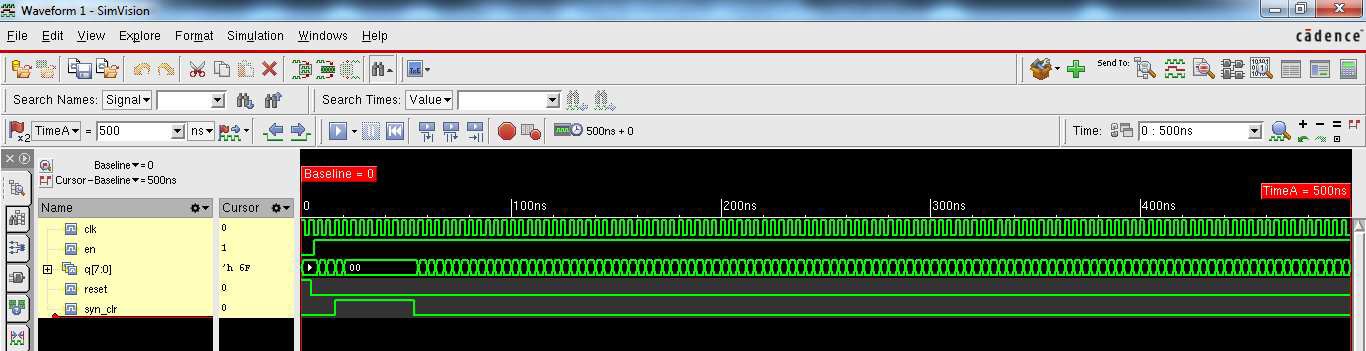

- Run the simulation: –

- Observe the waveforms: –

Post Credit

Faculty Advisor: Prof. Kamalakanta Mahapatra

Instructor: K Sudeendra, Teaching Assistants: S K Ram, J P Mohanty

VLSI Laboratory

The VLSI laboratory at ECE Department of NIT Rourkela is obliged towards the support and encouragement of Ministry of Electronics and Information Technology, Government of India. The overall activities is purely supported by the Special Manpower Development Program for Chips to System Design (SMDP-C2SD) project.

Sir pls post the comments for finding timedelay in cadence.

I think the upcoming tutorials will clear your doubts.