In the previous tutorial, we have presented a basic tutorial on Placement and Routing for ASIC. This tutorial is the first step towards Placement and Routing using INNOVUS tool. We will cover very basics of Placement and Routing using INNOVUS as it is a huge area and many tutorials are available on internet. Here, we will learn about Importing Files for PnR using INNOVUS. A basic Verilog code of a counter is considered here for implementation and we will use SCL180 nm library for our tutorials.

Required Files

- Design Netlist File (Verilog) – This file is created after the synthesis process and can either be generated using CADENCE Genus or SYNOPSYS Design Vision. Consider a simple Netlist file of a counter.v.

- Physical Library Files (LEF Files) – There are three kind of LEF files required which are

- Technology LEF File – This file contains the information about the Metal layers, Vias, design rules etc. for a certain technology. Here tsl180l4.lef is our technology LEF file.

- Standard Cell LEF File – This file contains the physical view of the standard cells in terms of current technology. Here tsl18fs120_scl.lef is our LEF file for standard cells.

- IO Cell LEF File – This file contains the physical view of the IO cells, corner cells, IO fillers in terms of current technology. Here tsl18cio250_4lm.lef is IO LEF file.

- View Definition File – This file is actually called Multi Mode Multi Corner (MMMC) view definition file. This file takes timing library files, Capacitance Tables and SDC files as inputs. Then creates Best and Worst case rc_corners for PVT analysis of the chip. Also, creates Max and Min libraries for timing and delay. Consider counter.view file as an example.

- IO Assignment file – This file is used for assigning the IO pins in a specific order. If this file is not used then tool will automatically assign the input output ports in convenient order. This file also places the IO pads and Corner cells.

- Power Constraint File – The Common Power Format (CPF) is a file that contains the information regarding power reduction techniques. For example, if multiple voltages are to be applied to reduce power then this should contain details about the multiple voltages.

Starting the Placement and Routing Step with CADENCE INNOVUS

1. The first step is to make a folder where all the required files will be stored and will be working directory. Say this folder is PnR_counter and another folder is library where all the library files are stored.

2. Second step is to invoke the CADENCE tool by source cadence.cshrc command.

3. Type innovus command to open the INNOVUS tool to proceed.

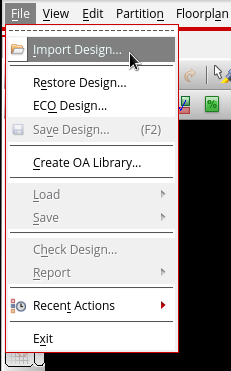

4. After the INNOVUS tool opens, first step is to import the design as shown below

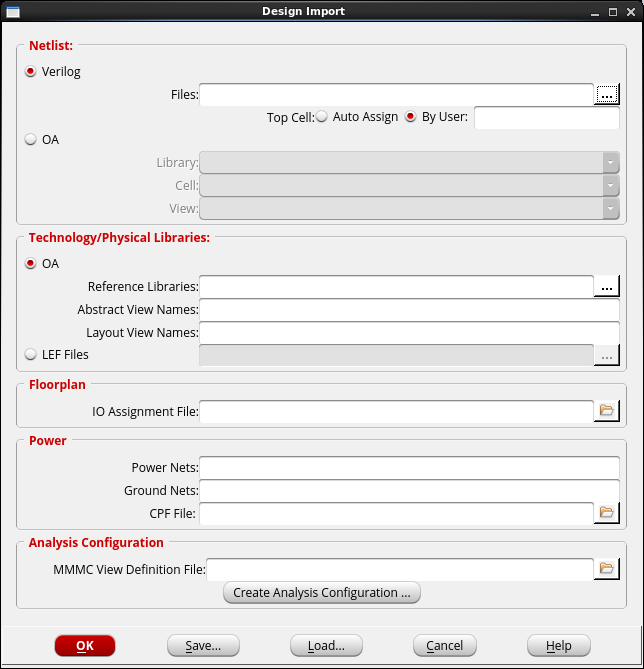

This will open the GUI window as

5. Verilog file – Design Netlist which is counter.v

6. LEF Files – LEF files must be uploaded in a sequence and the sequence is tsl180l4.lef, tsl18fs120_scl.lef and then tsl18cio250_4lm.lef

7. Power Net – VDD for Standard Cells and VDDO for IO, Ground Net – VSS for standard cells and VSSO for IO, CPF file is optional and not taken as input here.

8. IO assignment file – counter.io – preparation of this file will be discussed later.

9. MMMC file – counter.view – preparation of this file will be discussed later.

10. Once all the files given then next step is to Save this file import configuration in that folder as counter.globals. This is because in future for successive trails the counter.globals file can be loaded instead of importing all the files again individually.

###############################################################

# Generated by: Cadence Innovus 15.20-p005_1

# OS: Linux x86_64(Host ID vlsi-14.nitr.in)

# Generated on: Tue Mar 17 15:22:27 2020

# Design:

# Command: save_global OMP.globals

###############################################################

#

# Version 1.1

#

set ::TimeLib::tsgMarkCellLatchConstructFlag 1

set _timing_save_restore_compression_mode hybrid

set conf_qxconf_file {NULL}

set conf_qxlib_file {NULL}

set defHierChar {/}

set distributed_client_message_echo {1}

set distributed_mmmc_disable_reports_auto_redirection {0}

set gpsPrivate::dpgNewAddBufsDBUpdate 1

set gpsPrivate::lsgEnableNewDbApiInRestruct 1

set init_gnd_net {VSS VSSO}

set init_io_file {counter.io}

set init_lef_file {libraries/lef/tsl180l4.lef libraries/lef/tsl18fs120_scl.lef libraries/lef/tsl18cio250_4lm.lef}

set init_mmmc_file {counter.view}

set init_pwr_net {VDD VDDO}

set init_verilog {counter.v}

set latch_time_borrow_mode max_borrow

set lsgOCPGainMult 1.000000

set pegDefaultResScaleFactor 1.000000

set pegDetailResScaleFactor 1.000000

set report_inactive_arcs_format {from to when arc_type sense reason}

set timing_library_float_precision_tol 0.000010

set timing_library_load_pin_cap_indices {}

set timing_library_write_library_to_directory {}

set tso_post_client_restore_command {update_timing ; write_eco_opt_db ;}