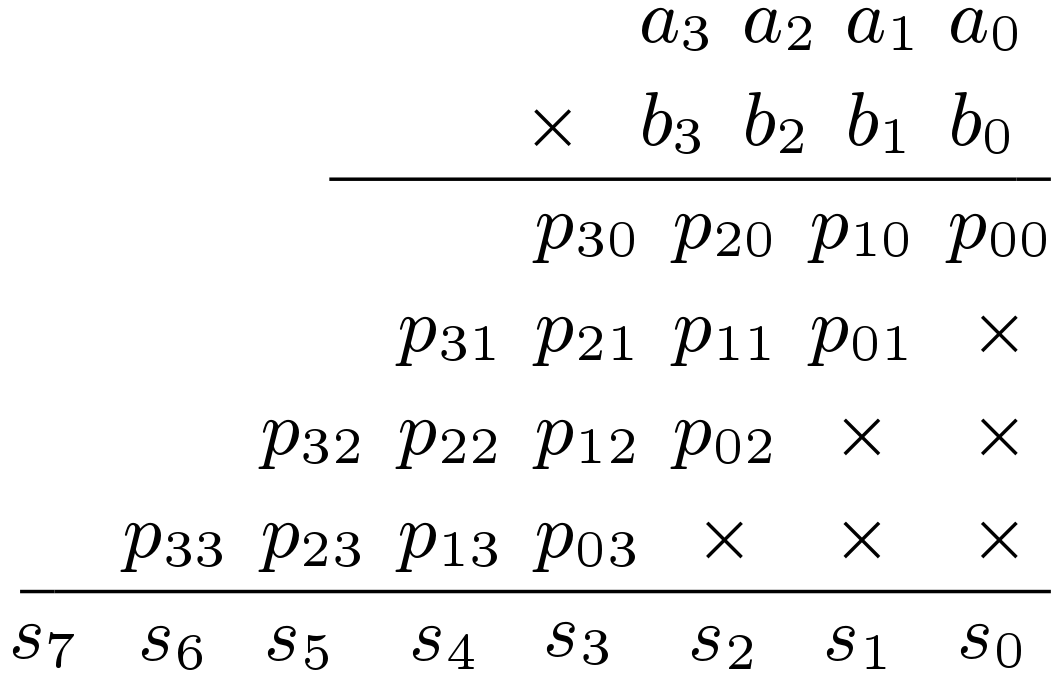

Array multiplier is very popular for multiplication of binary numbers. Array multiplier resembles the pen and paper method of multiplication process. Array multiplication process for two 4-bit unsigned numbers a and b is shown below.

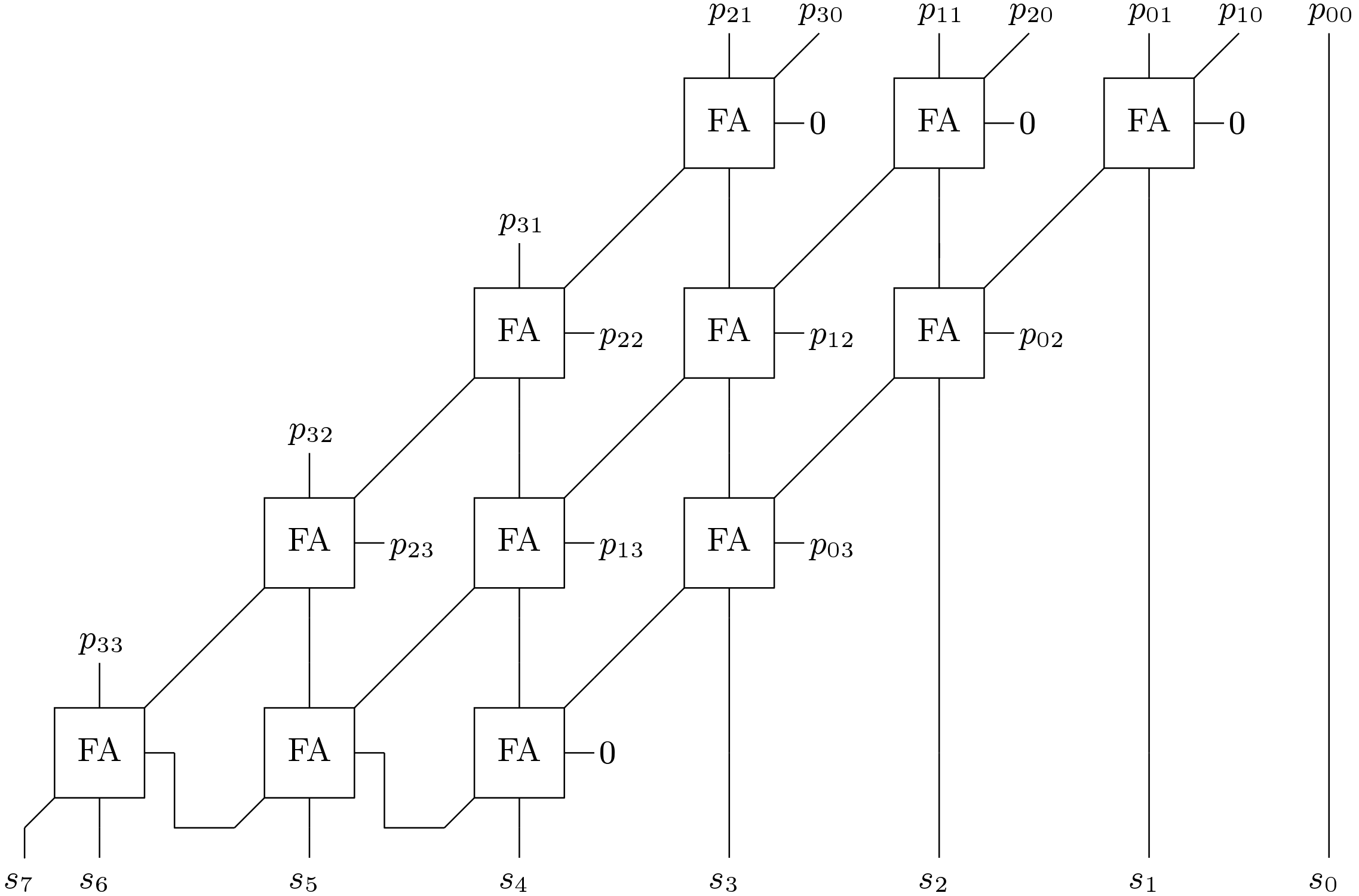

On the contrary to the sequential multiplier, array multiplier is parallel. A array of full adders are used for the multiplication process. For n-bit data width, total n(n-1) full adders are used in this multiplier. Carry outputs of a stage is added in the next stage to form a systolic architecture. But in the last stage carry is used in the same stage to reduce hardware. The architecture of the array multiplier is shown below.

Click here to download the Verilog code

you have made it so easy sir :)…this has helped me a lot !!!

kudos to you :))