In the previous tutorials, we have discussed how to simulate or synthesize a design using Synopsys or Cadence. Static Timing Analysis is a very important step in designing an digital design for ASIC. This tutorial is on performing Static Timing Analysis using Cadence Tempus.

1. Open the terminal

2. Source the cadence.cshrc

3. In this experiment, we are performing Static Timing Analysis using Cadence Tempus. STA can be performed on both pre-layout and post-layout netlist. In this experiment we perform pre-layout STA. The files required for this experiment is: –

a. Synthesized netlist (from synthesis tool : Design compiler or RTL compiler (Genus))

b. Timing library files (.lib file used in synthesis in RTL compiler)

4. In a ASIC lab directory, create design_netlist.v using synthesis with constraints.

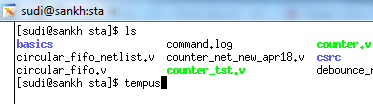

5. Open the tempus (Cadence STA tool) using command as below: –

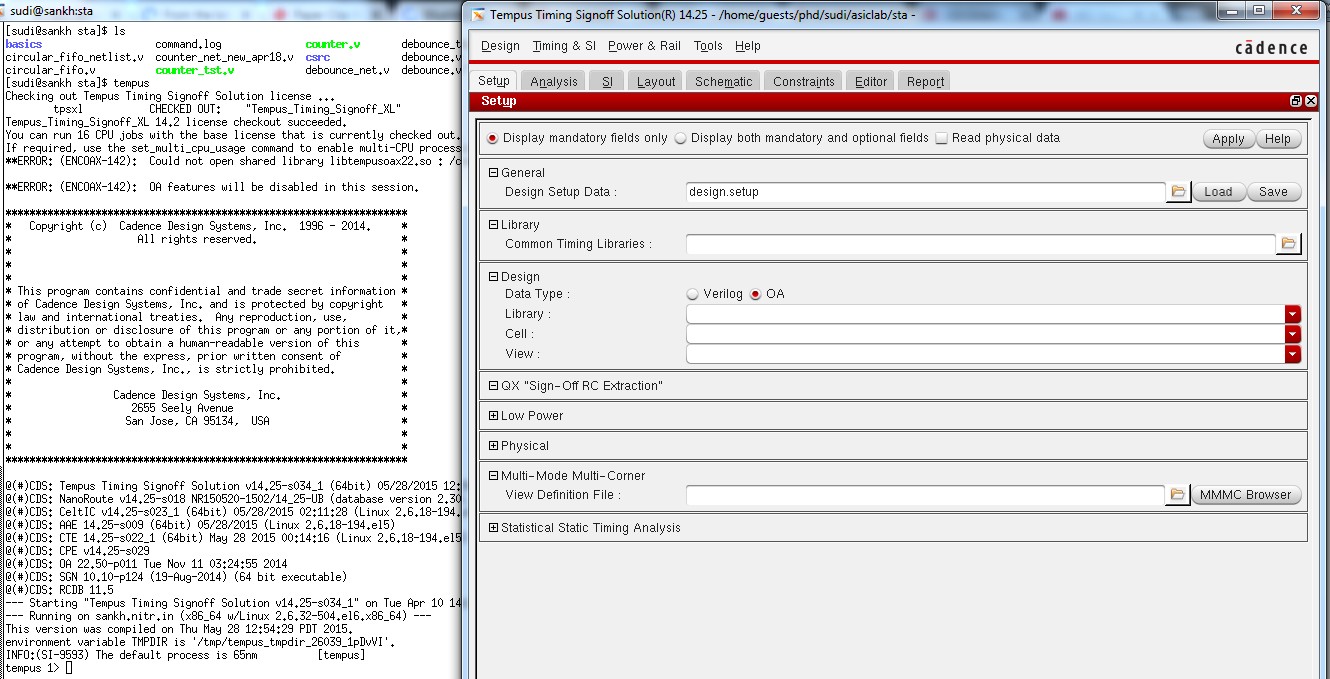

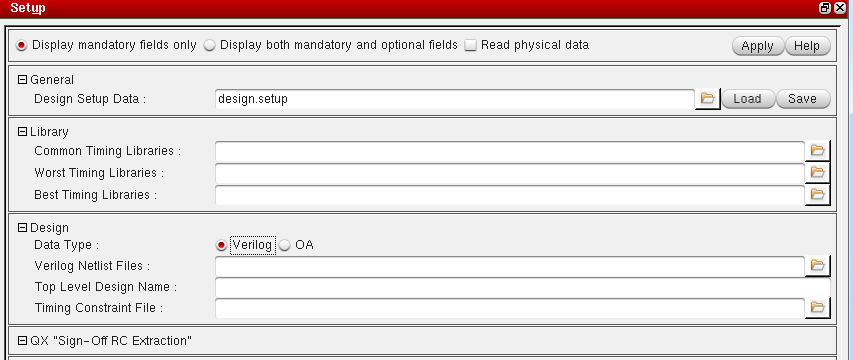

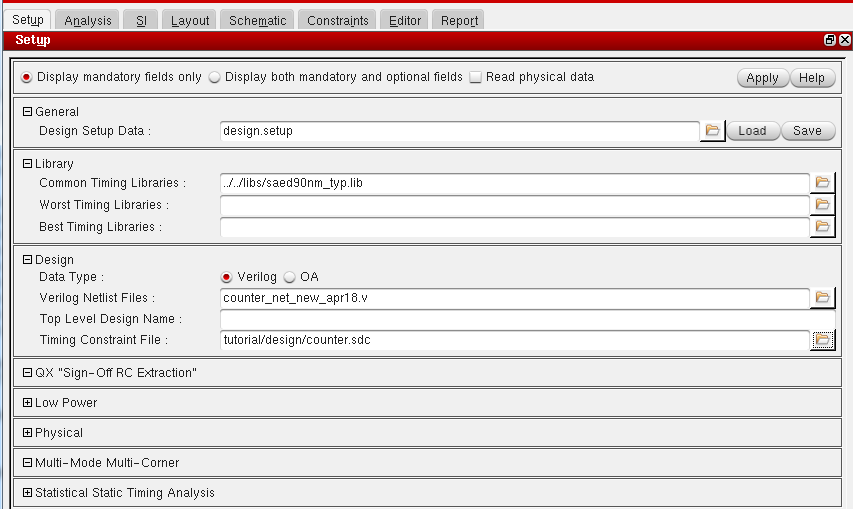

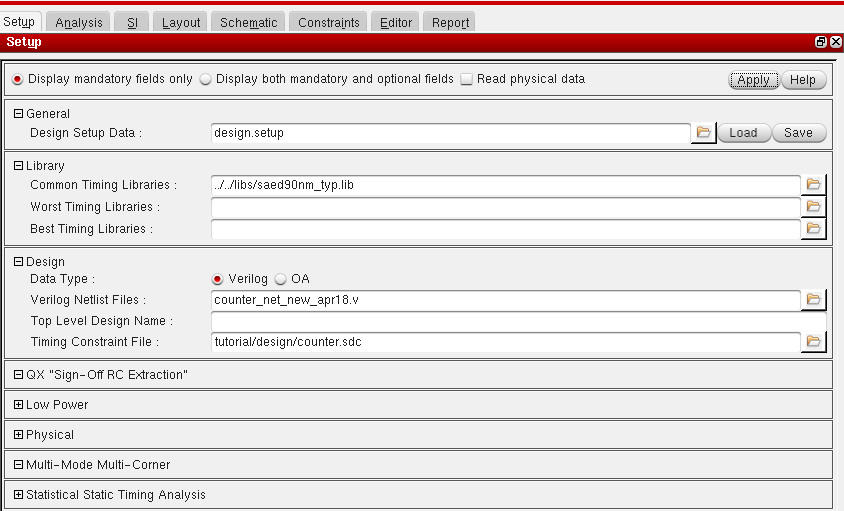

6. Select the: – Display mandatory fields only and Data type to Verilog as below: –

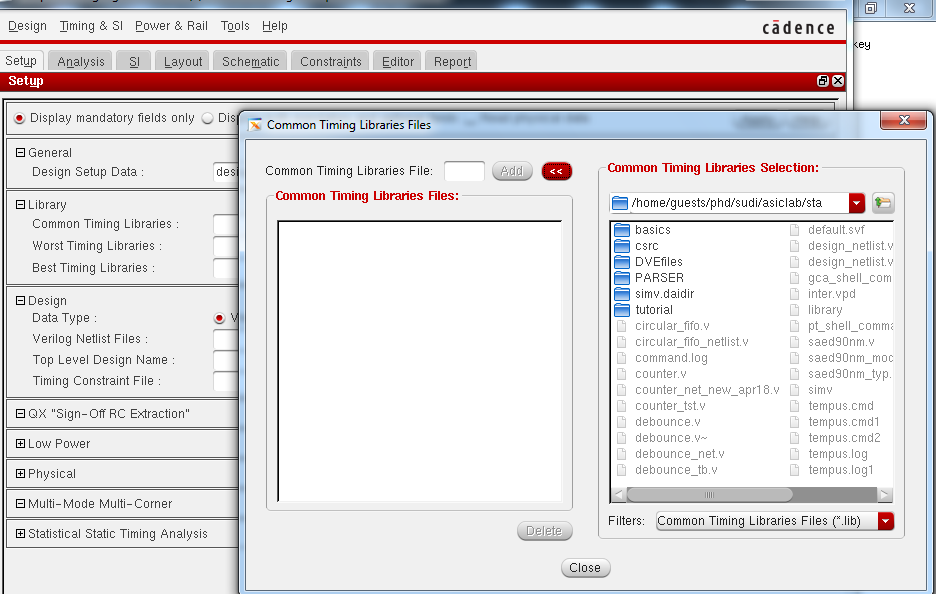

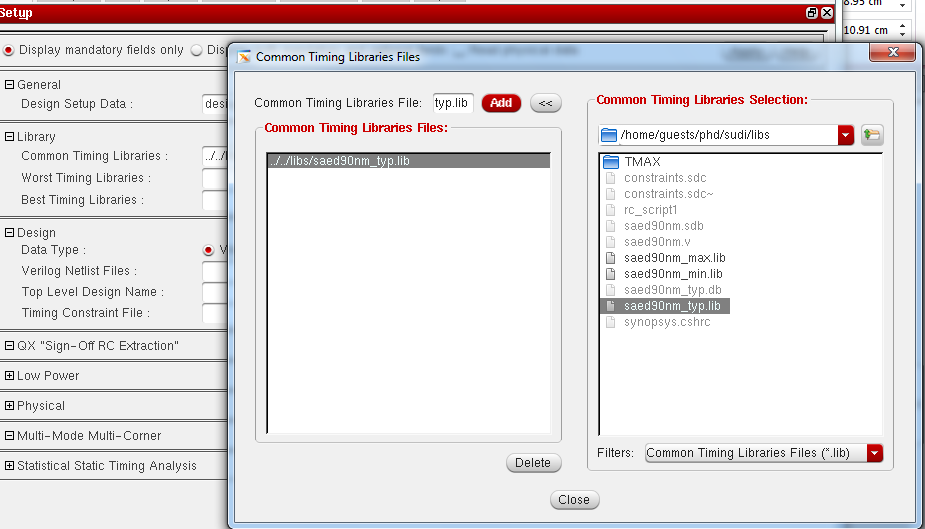

7. Click on common timing libraries, browse and select .lib file used for synthesis from libs folder or where ever you have saved .lib file as below: –

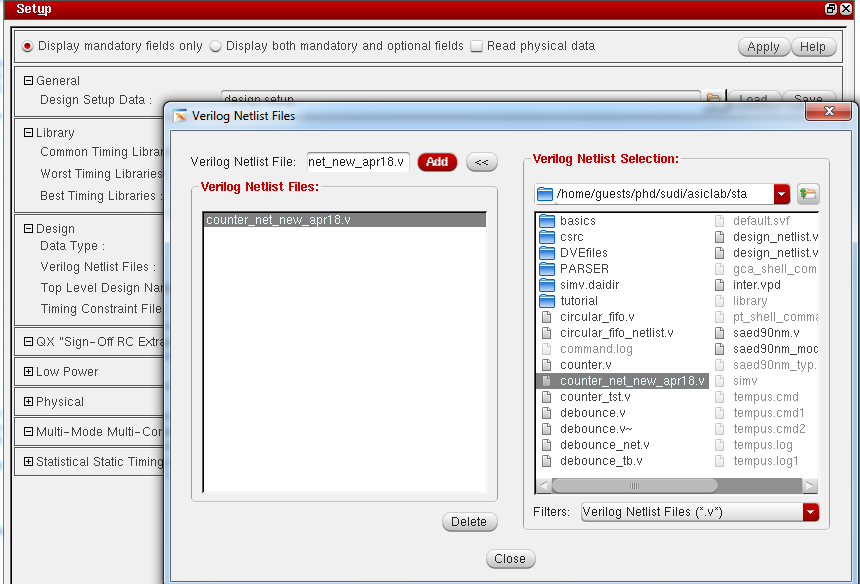

8. Select the gate level netlist as below: –

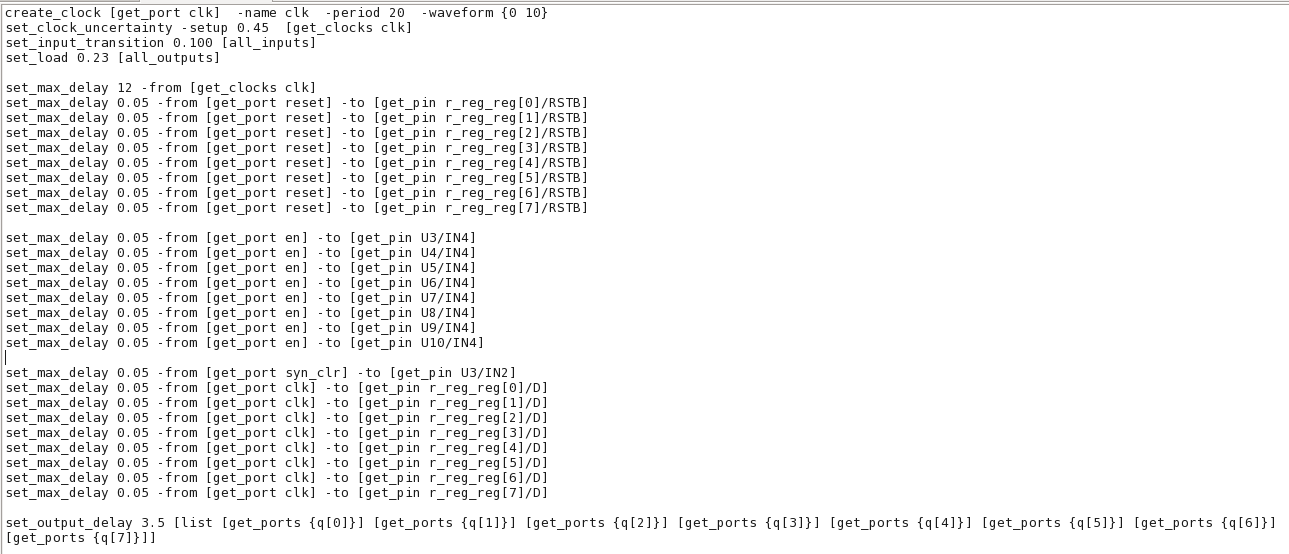

9. Read the timing constraints file as below (constraints are designed for gate level netlist, understand netlist by opening netlist in gedit): –

10. Click on Apply: –

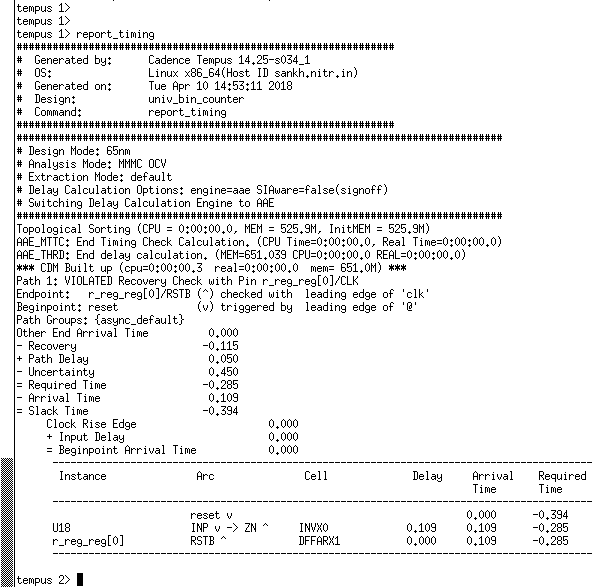

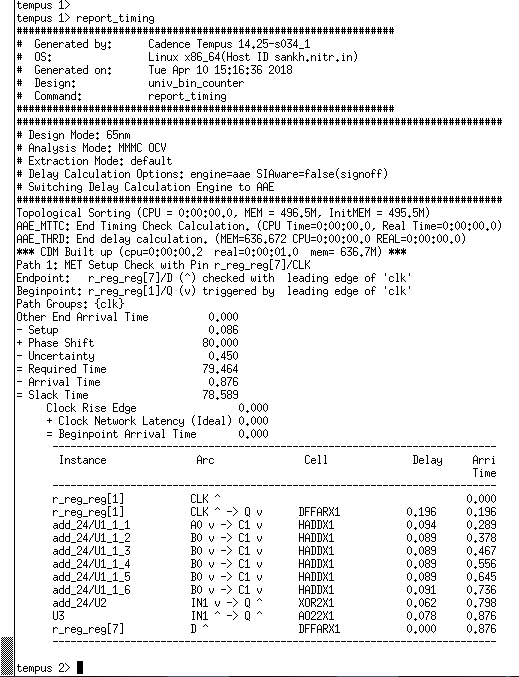

11. Go to terminal and type report_timing as below: –

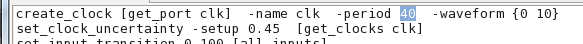

12. Observe that slack is negative. So open the timing cosntraints file. Increase the clk period to 40 in the constraints file as : –

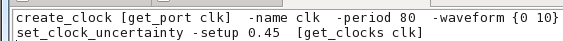

Save the constraints file. Click on browse to timing constraints file and delete the constraints file and reselect the saved file (updated with clk period 40 or 80). Just remove all set_max and other constraints and just keep the only two statements related to clk as below :-

13. Report_timing in tempus and find positive slack: –

14. Keep experiment with adding set_max constraints and work out a optimal postive slack.

Post Credit

Faculty Advisor: Prof. Kamalakanta Mahapatra

Instructor: K Sudeendra, Teaching Assistants: S K Ram, J P Mohanty

VLSI Laboratory

The VLSI laboratory at ECE Department of NIT Rourkela is obliged towards the support and encouragement of Ministry of Electronics and Information Technology, Government of India. The overall activities is purely supported by the Special Manpower Development Program for Chips to System Design (SMDP-C2SD) project.