Logic Equivalence Checking is a very important step to be performed after synthesis step. This operation checks for similarity between the original code and the synthesis Netlist. This operation is important as the synthesis tool may trim or remove some unused and unconnected ports and redundant logics. The steps of performing Logic Equivalence Checking in Cadence is given below.

1 Open the terminal

2. Source the cadence.cshrc

3. In this experiment, we are performing equivalence checking. RTL code and synthesized gate-level netlist are compared structurally using LEC tool (Logical Equivalence Checking). We use Cadence Conformal tool in this experiment.

4. In a ASIC lab directory, create design.v. Create the testbench.v and verify the design. Synthesize the design in GENUS (with or without constraints) and save the netlist. Perform gate-level simulations and verify for functionality. In LEC, we are comparing design (RTL code) and gate level netlist statically.

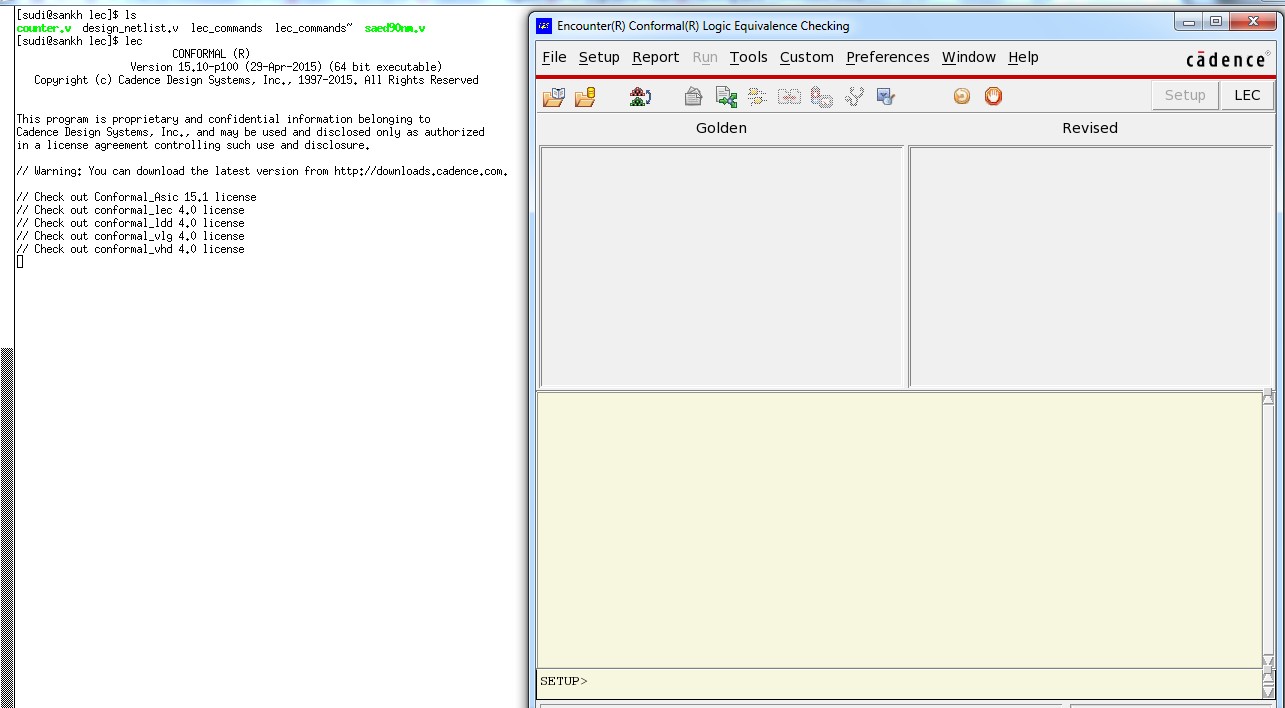

5. Open the conformal using command lec as below: – (execute the following commands in the setup command line)

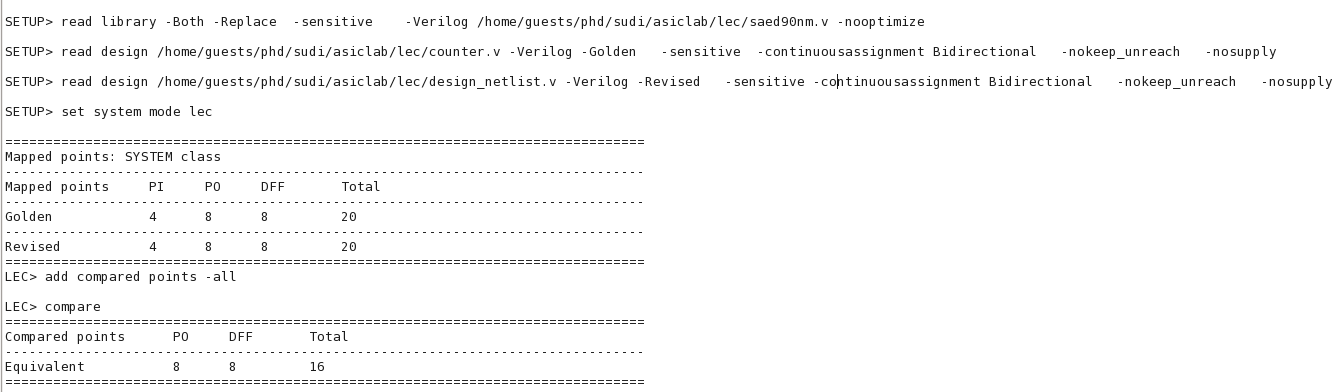

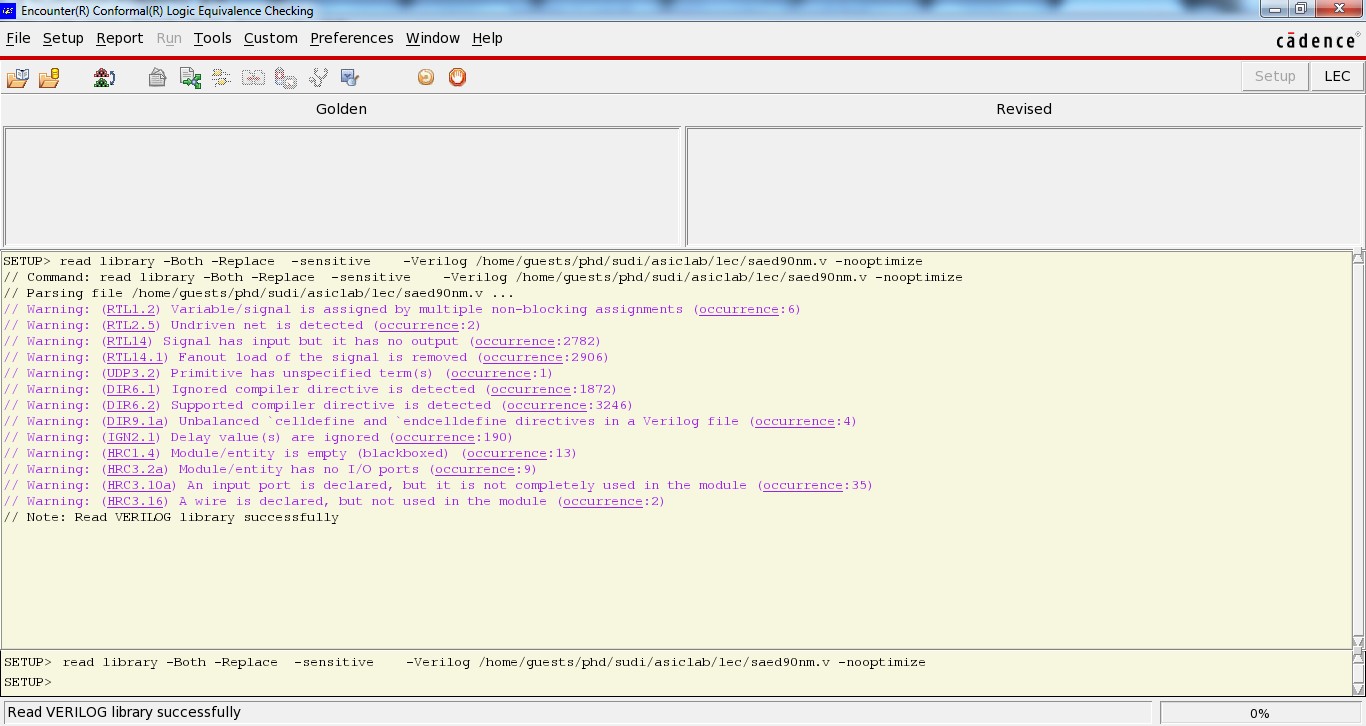

6. Read Library:-

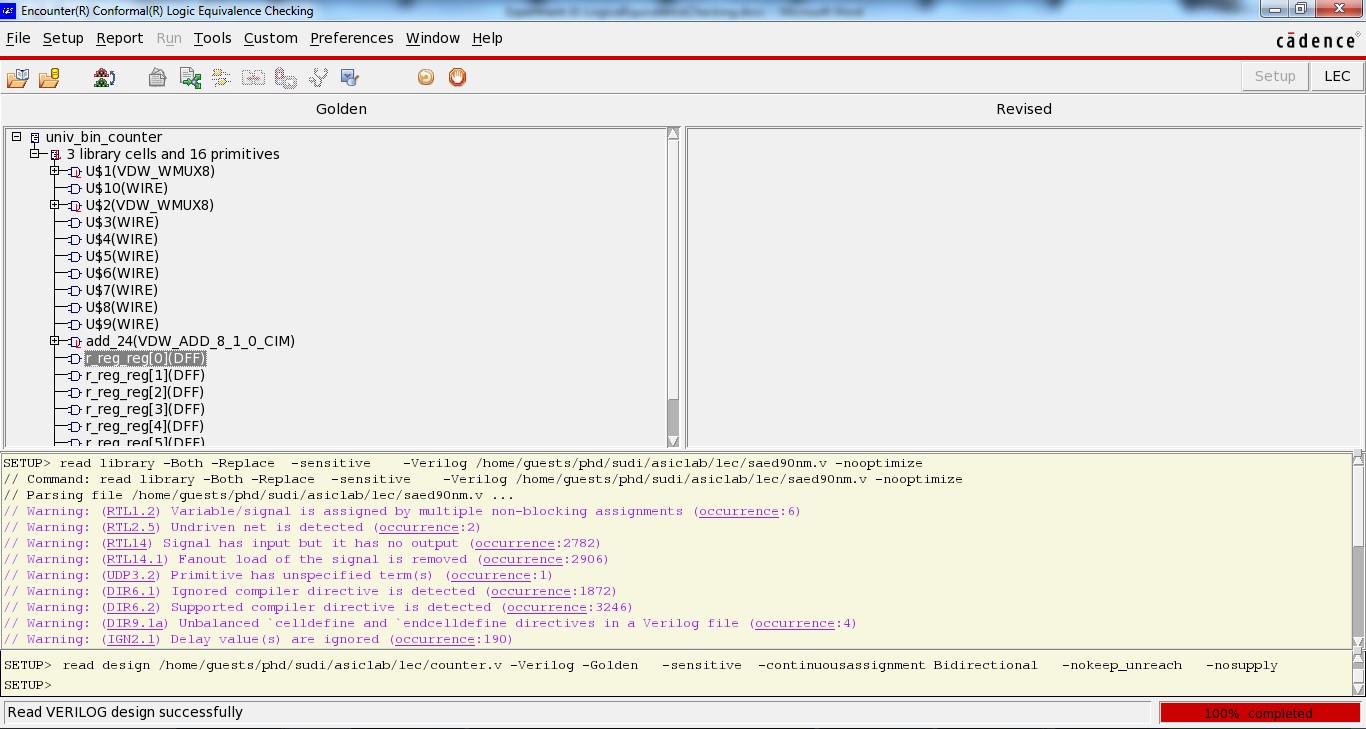

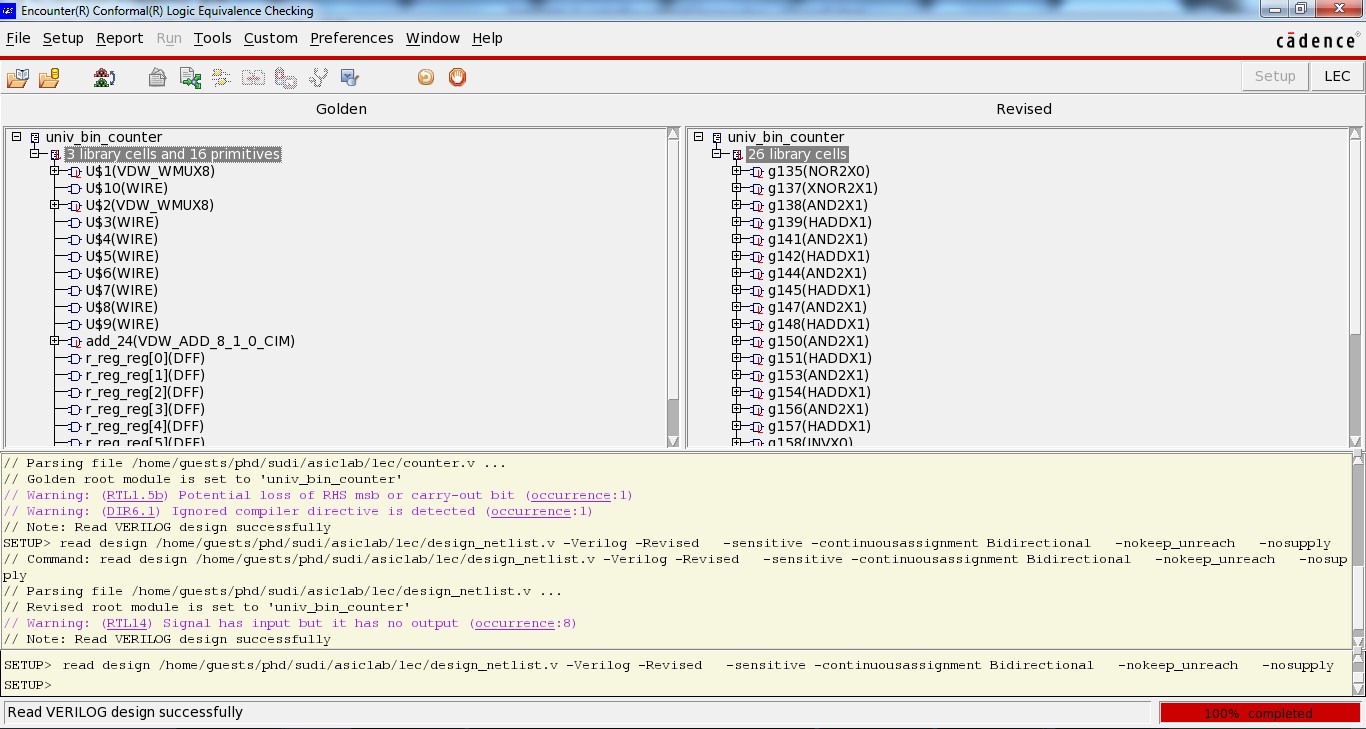

7. Read Golden design file (RTL code): –

8. Read revised design (gate_level_netlist): –

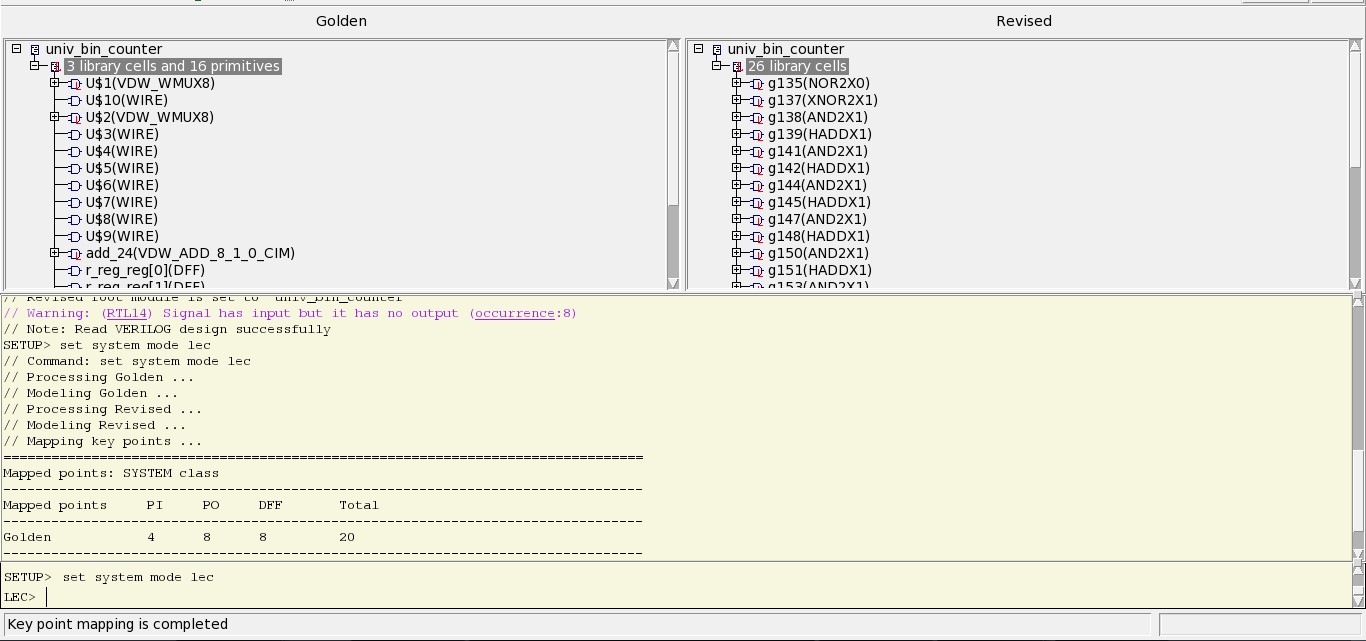

9. Change the mode from ‘SETUP’ to ‘LEC’ as Below

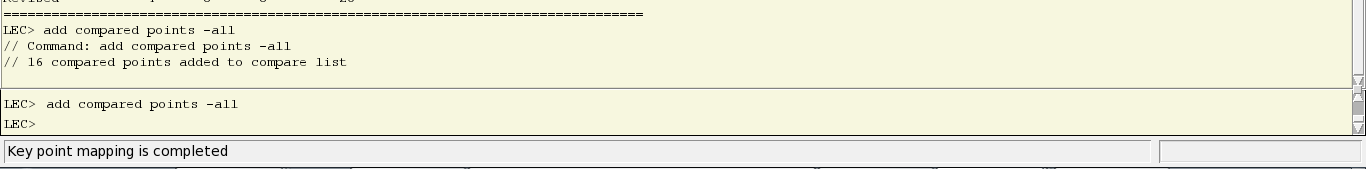

10. Add all compare points: –

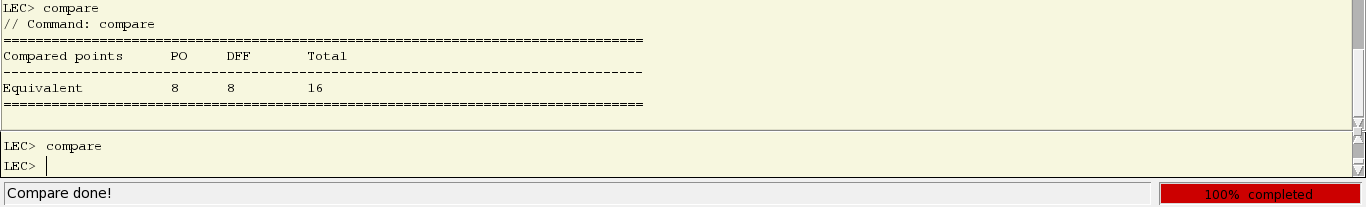

11. Compare the golden (RTL) and revised (gate level netlist or synthesized netlist): –

12. Compare done. Generally successful comparison is not easy. For large and medium scale designs, we get unsucessful comparisons. Right click on design name (both golden and revised) and by looking at schematic we can debug the mismatches.

13. Perform the equivalence checking for all the designs you have done in lab (FIFO etc).

Post Credit

Faculty Advisor: Prof. Kamalakanta Mahapatra

Instructor: K Sudeendra, Teaching Assistants: S K Ram, J P Mohanty

VLSI Laboratory

The VLSI laboratory at ECE Department of NIT Rourkela is obliged towards the support and encouragement of Ministry of Electronics and Information Technology, Government of India. The overall activities is purely supported by the Special Manpower Development Program for Chips to System Design (SMDP-C2SD) project.