This tutorial is in continuation with our previous tutorial on Genus Synthesis Without Constraints (Timing Constraints). The timing constraints are written in Synopsys Design Constraint (SDC) file.

1. Open the terminal and type csh

2. Source the cadence.cshrc.

3. In ASIC lab folder, make a new directory. In this, make design.v (in this example counter.v). In this experiment, we perform the synthesis with basic constraints. In the previous experiment, synthesis was performed without constraints. Follow the procedure of previous experiment (Synthesis-I) and after “elaborate” command insert timing constraint’s source file and continue the synthesis (detailed below).

4. Execute genus –gui for invoking the EDA Synthesis tool and follow the instructions below.

[sudi@sankh]![]() genus –gui

genus –gui

genus@root:> read_libs saed90nm_typ.lib

genus@root:> read_hdl -v2001 counter.v

genus@root:> elaborate

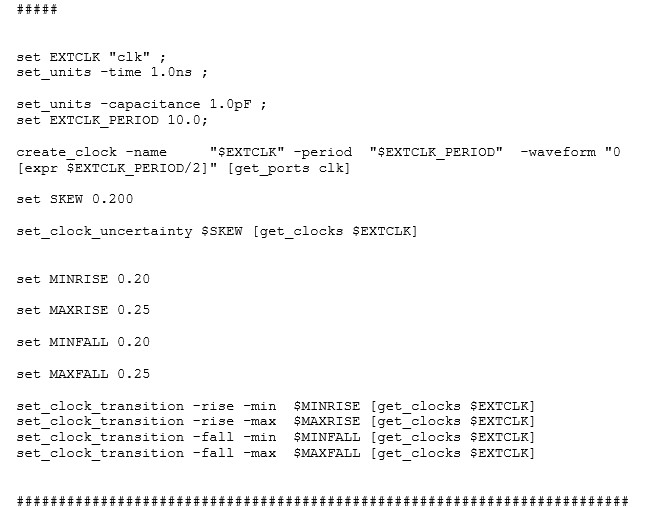

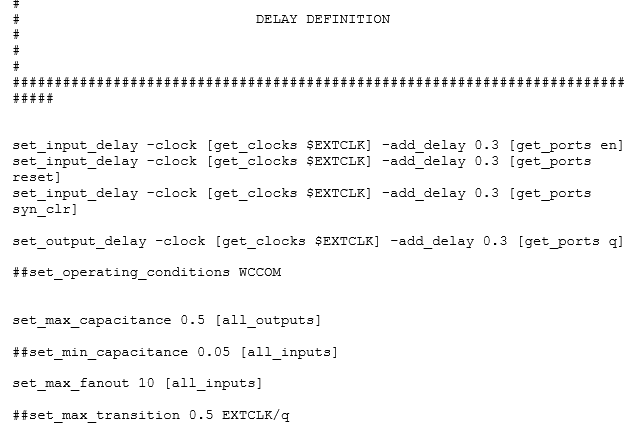

5. A constraint file is sourced to insert constraints shown below.

Change the constraints accordingly for your designs (input, output and clock). Perform synthesis for FIFO, Debouncing circuit etc.

genus@root:> source constraints1.sdc

genus@root:> synthesize -to_mapped

6. Save the gate level netlist

genus@root:> write_hdl > counter_constr_netlist.v

7. Find the new netlist file created in the working directory.

8. Record the area, timing and power by following the below commands (following the text file name that will be saved in the working directory)

genus@root:> report_units

genus@root:> report_timing > timing

genus@root:> report_area > area

genus@root:> report_power > power

genus@root:> report_utilization

genus@root:> report_sequential

7. Do the synthesis and report timing. Change the constraints and check for the slack. And compare the area, timing, power for unconstrained and constrained synthesized designs (vary the constraints).

8. Simulate the design as you did in earlier experiment. Check the simulation using this netlist file. (Blindly don’t follow the manual. Give the correct path based on where you have the libs folder copied. Use the command “pwd” to get path)

[sudi@sankh]$ ncverilog counter_tst.v counter_constr_netlist.v +access+rw -v saed90nm.v +gui

For more details check the Genus_gui document in the installed folder

Post Credit

Faculty Advisor: Prof. Kamalakanta Mahapatra

Instructor: K Sudeendra, Teaching Assistants: S K Ram, J P Mohanty

VLSI Laboratory

The VLSI laboratory at ECE Department of NIT Rourkela is obliged towards the support and encouragement of Ministry of Electronics and Information Technology, Government of India. The overall activities is purely supported by the Special Manpower Development Program for Chips to System Design (SMDP-C2SD) project.