Floating point multiplication is comparatively easy than the floating point addition algorithm but off course consumes more hardware than fixed point multiplier circuit. Major hardware block is the multiplier which is same as fixed point multiplier. This multiplier is used to multiply the mantissas of the two numbers. A floating point multiplication between two numbers ![]() and

and ![]() can be expressed as

can be expressed as

![]()

Thus it can be said that in a floating point multiplication, mantissas are multiplied and exponents are added. The major steps for a floating point division are

- Extract the sign of the result from the two sign bits.

- Add the two exponents (

). Subtract the bias component from the summation.

). Subtract the bias component from the summation. - Multiply mantissa of

(

(  ) by mantissa of

) by mantissa of  (

(  ) considering the hidden bits.

) considering the hidden bits. - If the MSB of the product is

then shift the result to the right by 1-bit.

then shift the result to the right by 1-bit. - Due to this, the exponent is to be incremented according to the one bit right shift.

Floating point multiplication can be more clearer with an example. Lets discuss a multiplication operation between two numbers ![]() and

and ![]() . The result of the multiplication operation is

. The result of the multiplication operation is ![]() .

.

Example: Floating Point Multiplication

- Representation: The input operands are represented as

and

and  .

. - Sign extraction: As both the numbers are positive then sign of the output will be positive. Thus

.

. - Exponent addition: The value of

and

and  . Thus result of the addition is

. Thus result of the addition is  . The bias is subtracted from this value. Thus new value of

. The bias is subtracted from this value. Thus new value of  is

is  .

. - Mantissa multiplication: Multiply the mantissas by any multiplicative algorithms used in the fixed point arithmetic. The width of the product is 24-bits but the final output is truncated to 11-bits. The 13-bits of the product starting from the MSB is

.

. - Generally the 11-bits from the LSB are the required result but here the MSB is

this indicate that the result is greater than

this indicate that the result is greater than  . Thus this value is shifted right by 1-bit and the new result is

. Thus this value is shifted right by 1-bit and the new result is  . The final value of the mantissa (

. The final value of the mantissa ( ) is

) is  excluding the hidden bit.

excluding the hidden bit. - This normalization step must reflect on exponent correction. The value of the exponent is corrected by an increment corresponding to a right shift. The new value of the exponent (

) is

) is  .

. - The final result is

which is equivalent to

which is equivalent to  in decimal.

in decimal.

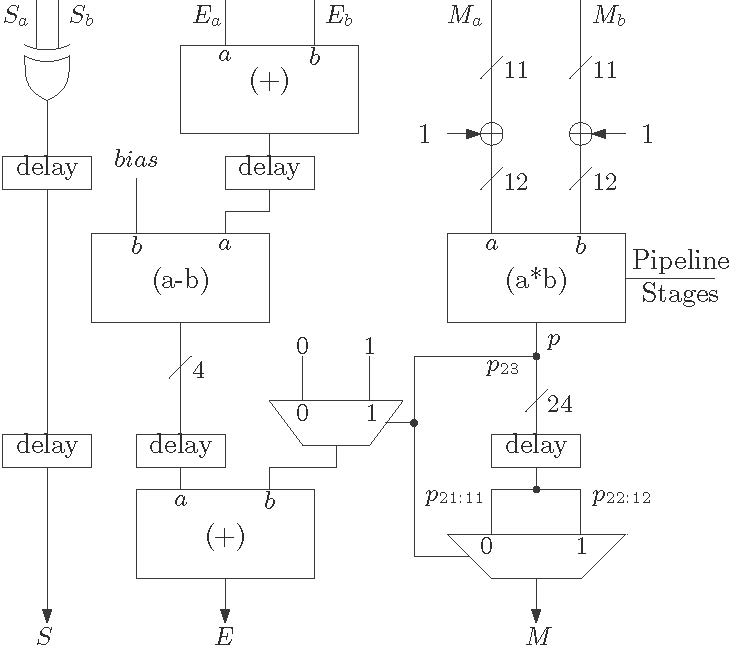

A simple architecture for floating point multiplication is shown below in Figure 1 . The addition of the exponents is done by a 5-bit adder as addition result can be greater than 15. The subtraction of the bias element can be done by another 5-bit adder. There is another 4-bit adder used the design which is actually an incrementer. The major hardware block is the multiplier block. The multiplier used here is a 12-bit unsigned multiplier and that can be any multiplier circuit as discussed in the blog for fast multiplication. If MSB of the product is ![]() then the output is normalized by right shifting. Here this right shift is simply achieved by using MUXes. In this case, as the hidden bit is also considered, the result will be always less than

then the output is normalized by right shifting. Here this right shift is simply achieved by using MUXes. In this case, as the hidden bit is also considered, the result will be always less than ![]() . Thus only the MSB is checked. Pipeline registers are also must be inserted according to the pipe lining stages of the multiplier.

. Thus only the MSB is checked. Pipeline registers are also must be inserted according to the pipe lining stages of the multiplier.