Code coverage is a basic coverage type which is collected automatically. It tells you how well your HDL code has been exercised by your test bench. In other words, how thoroughly the design has been executed by the simulator using the tests used in the regression.

Functional coverage measures how well the functionality of the design has been covered by your test bench. In functional coverage user has to define the functionality to be measured through coverage.

There are different categories of code coverage.

- Statement coverage

- Block coverage

- Conditional/Expression coverage

- Branch/Decision coverage

- Toggle coverage

- FSM coverage

Code Coverage using Cadence Tool

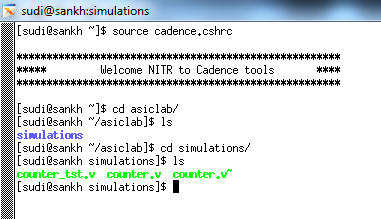

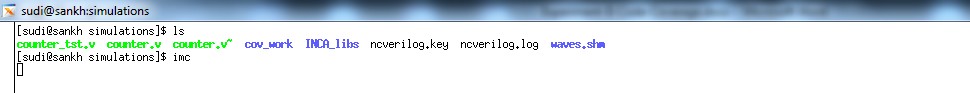

- Open the terminal

- Source the cadence.cshrc

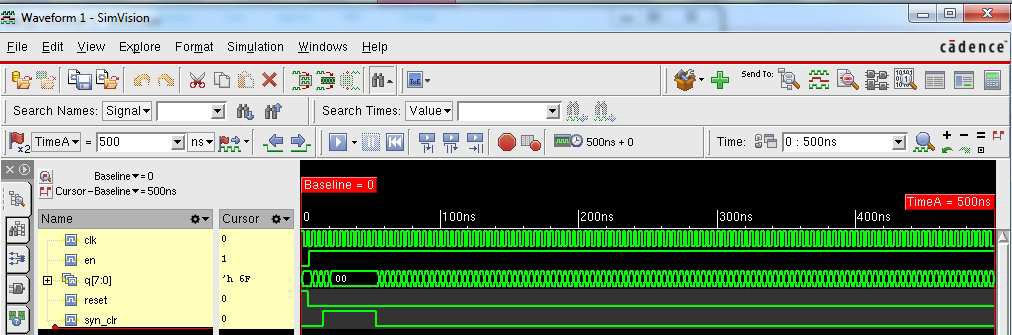

- In a ASIC lab directory, make design.v and testbench.v ready. Clear the syntax errors, simulate and confirm the functionlity thorugh simvision simulations. (Follow the tutorial for simulation in CADENCE).

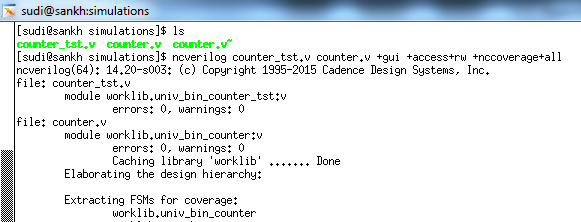

- Execute the following command for coverage: –

Other Commands are………………….

- ncverilog counter_tst.v counter.v +access+rw +nccoverage+all +gui

- ncverilog counter_tst.v counter.v +access+rw +nccoverage+line +gui

- ncverilog counter_tst.v counter.v +access+rw +nccoverage+branch +gui

- ncverilog counter_tst.v counter.v +access+rw +nccoverage+toggle +gui

- ncverilog counter_tst.v counter.v +access+rw +nccoverage+fsm +gui

- Simulate completely: –

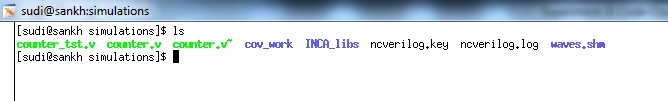

- Observe the “cov_work” folder created in the directory: –

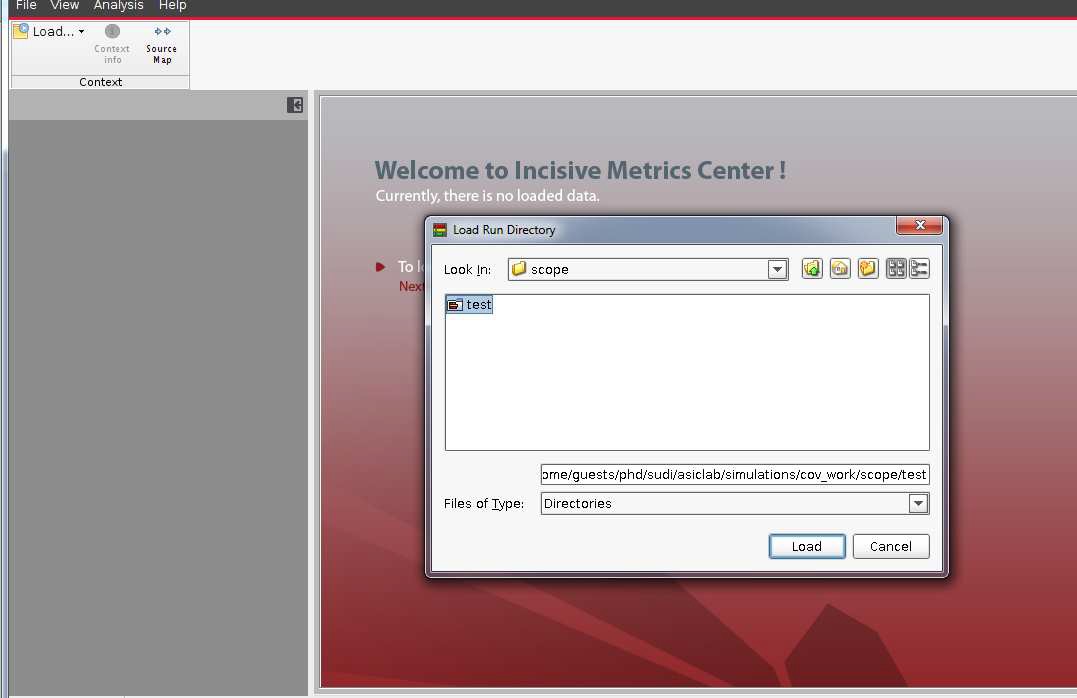

- Open the Incisive Metrics Coverage tool (IMC): imc &

- Load the test file from the folder “cov_work”

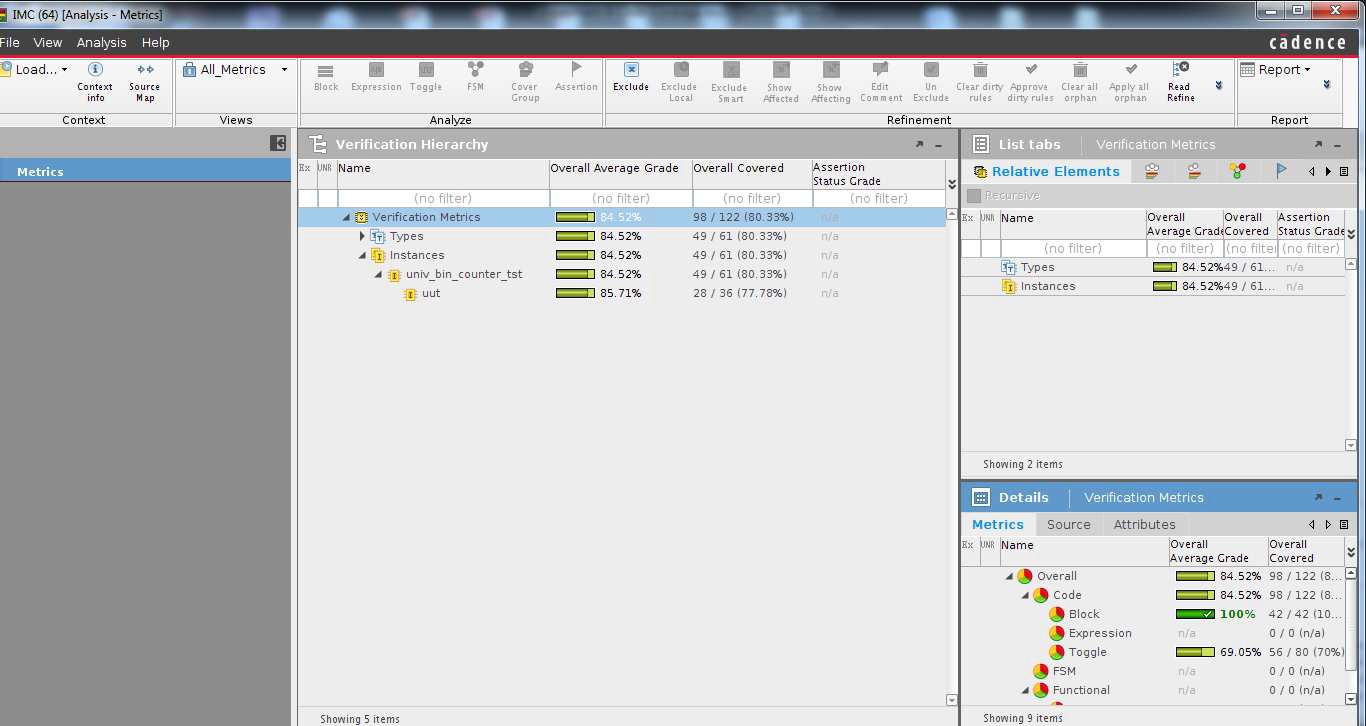

- IMC opens the coverage metrics analysis: –

- Write the better testbenches for all the designs : – counter, FIFO, Debouncing circuit, Edge detector to get 96% coverage in all categories: – FSM, toggle, block and expression.

Post Credit

Faculty Advisor: Prof. Kamalakanta Mahapatra

Instructor: K Sudeendra, Teaching Assistants: S K Ram, J P Mohanty

VLSI Laboratory

The VLSI laboratory at ECE Department of NIT Rourkela is obliged towards the support and encouragement of Ministry of Electronics and Information Technology, Government of India. The overall activities is purely supported by the Special Manpower Development Program for Chips to System Design (SMDP-C2SD) project.