Here, tutorial on simulation of Verilog file using Synopsys EDA tool is given. Also, synthesis using Deign Vision tool is also shown. The reader find this tutorial on Synopsys Simulation and Synthesis very useful.

1. Open the terminal

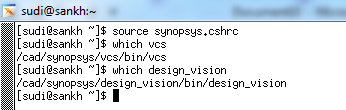

2. Source the synopsys.cshrc

3. Check whether the commands are working as below. Terminal will echo the installation path of tools as below.

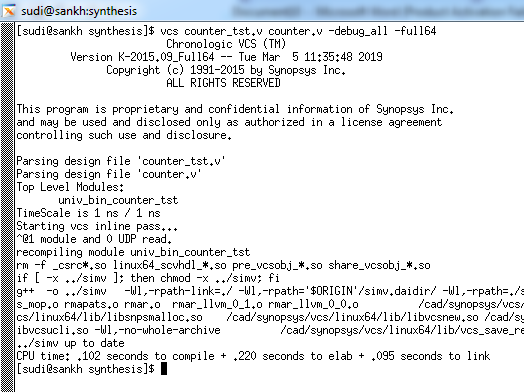

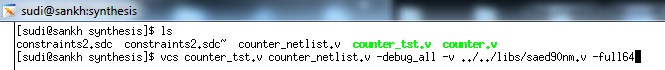

4. Create a directory for saving files as below and simulate using VCS (VCS is simulation tool from synopsys similar to cadence ncverilog (ncsim) . The command line is shown below: –

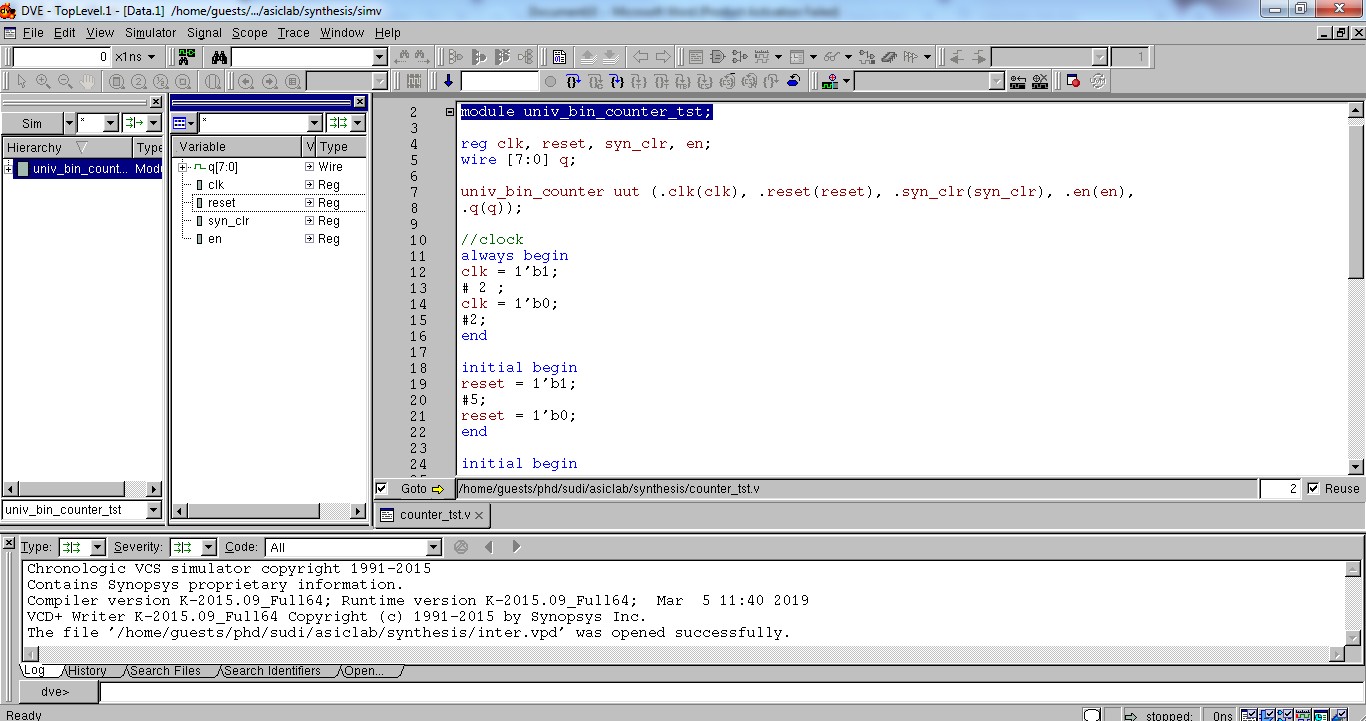

5. Observe the executable file “simv” is created as shown below and execute simv. (./simv –gui)

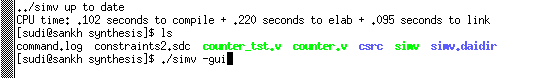

6. Execution will open a simulation tool as below: –

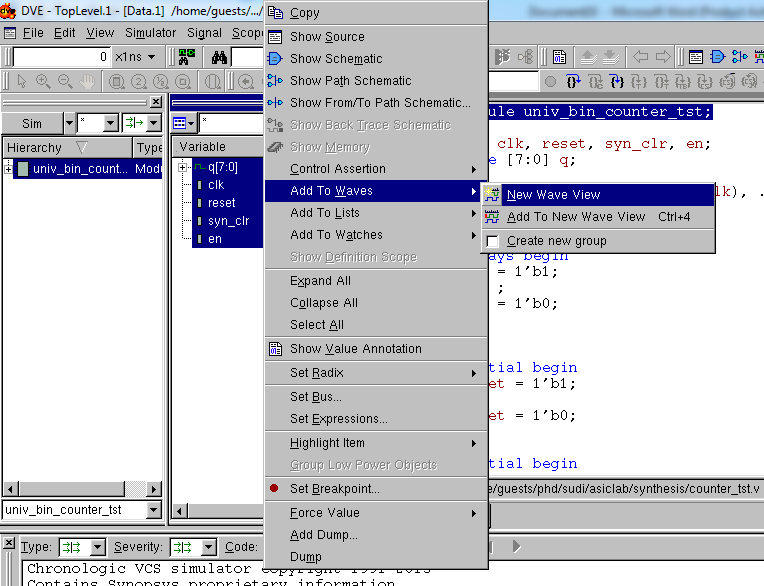

7. Select the signals and send them to waveform window as below: –

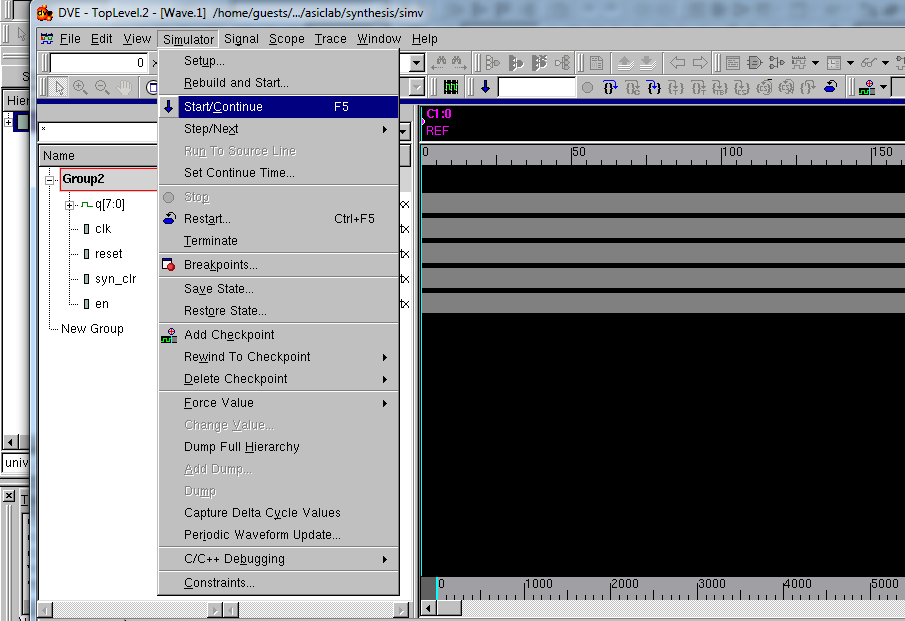

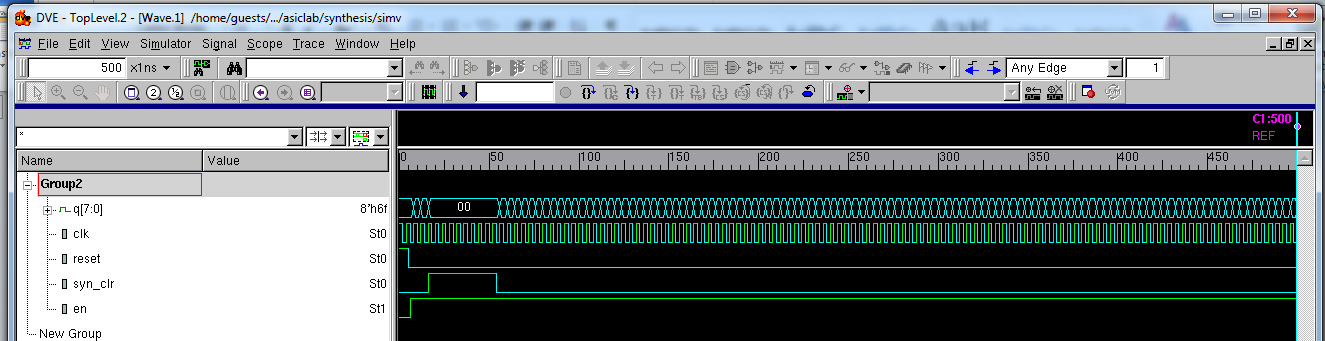

8. Run the simulation as below: –

9. Similarly we can simulate all the designs using Synopsys VCS and perform coverge anlaysis using cmView.

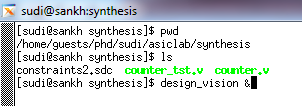

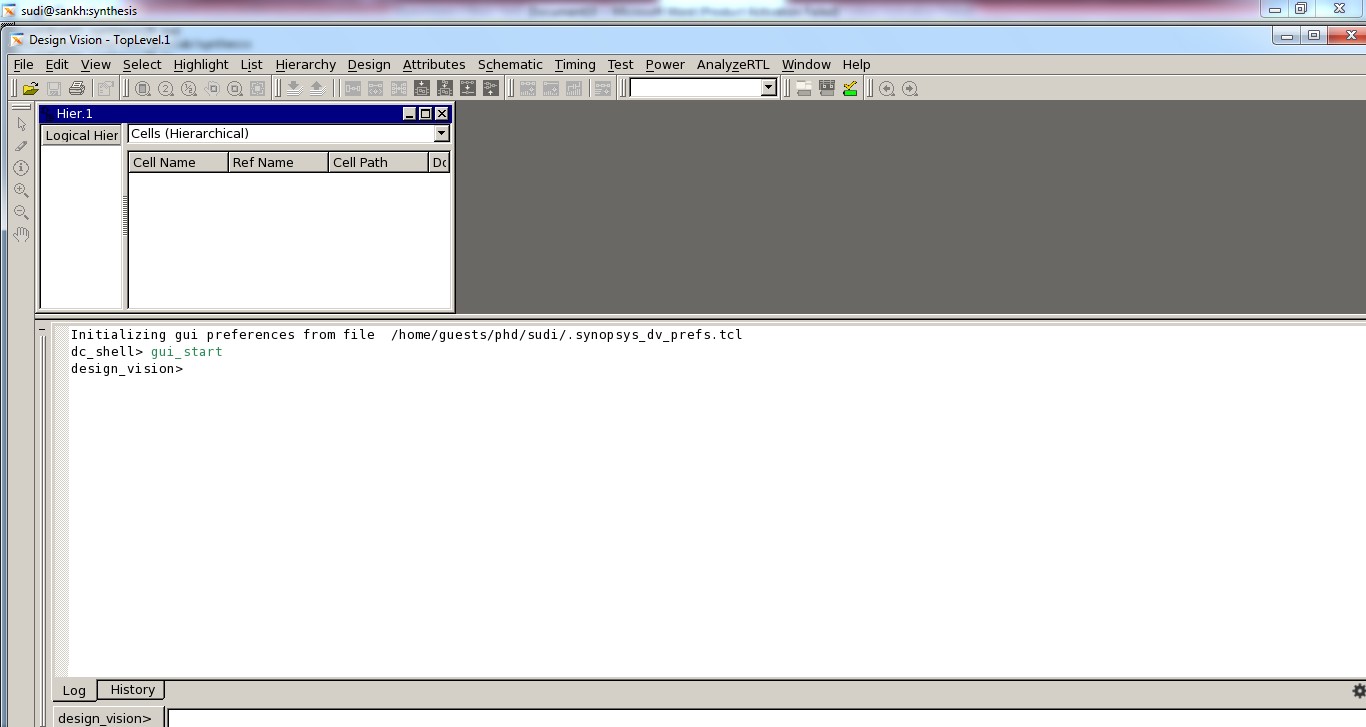

10. Synthesis: – Create a directory for saving files as below and Invoke the design_vision tool as below: –

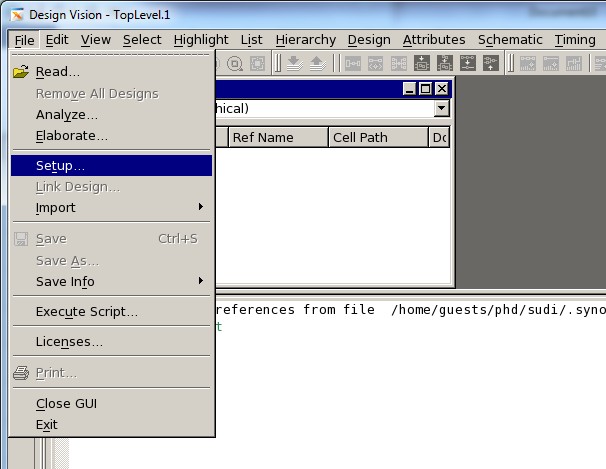

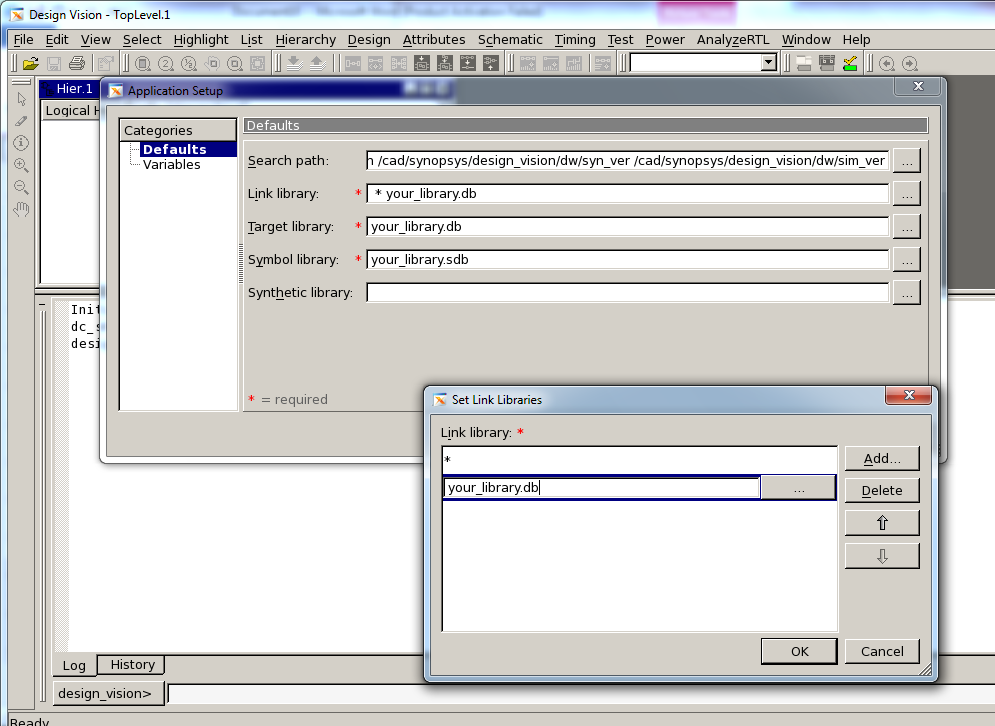

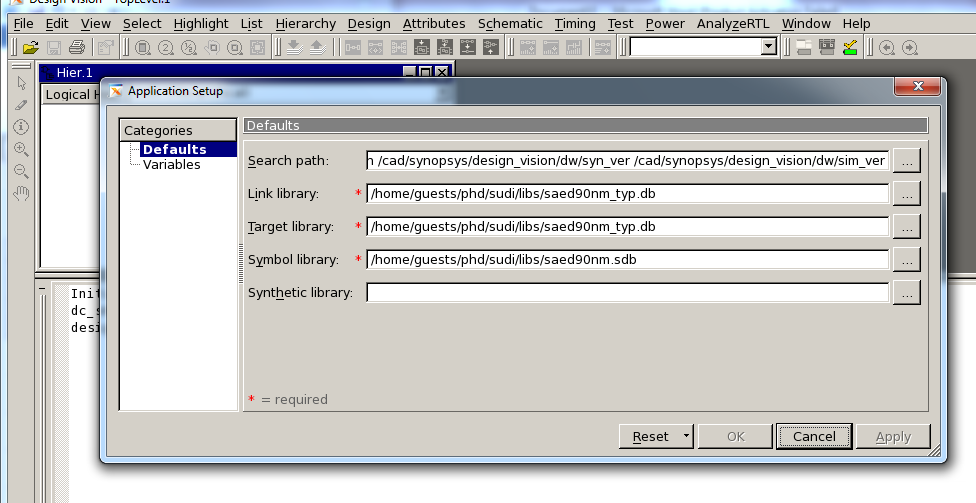

11. Add the librarries, (similar to .lib files used in Cadence genus). Here we add .db and .sdb files as below: –

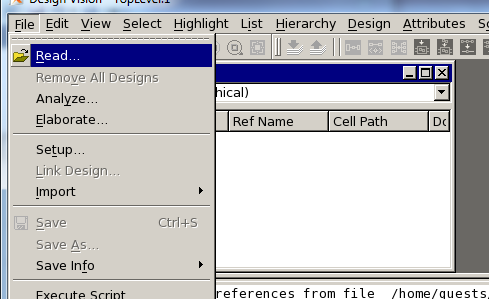

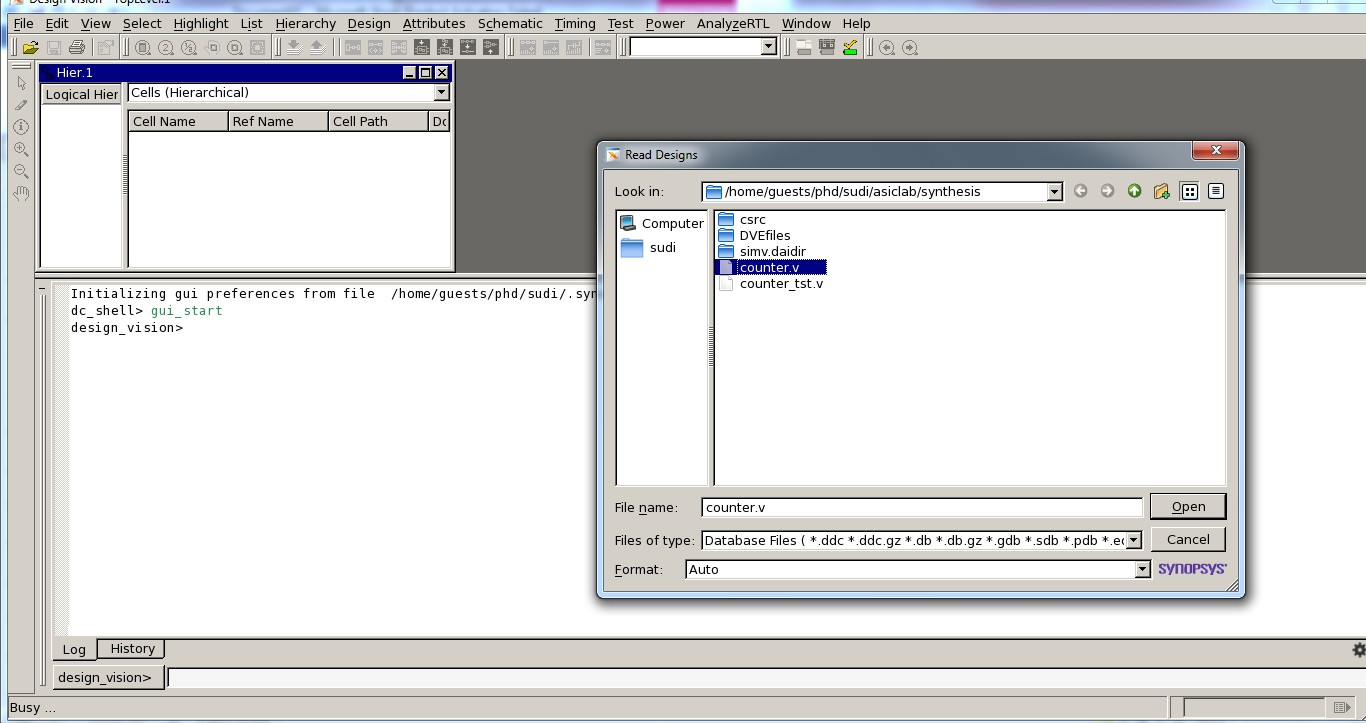

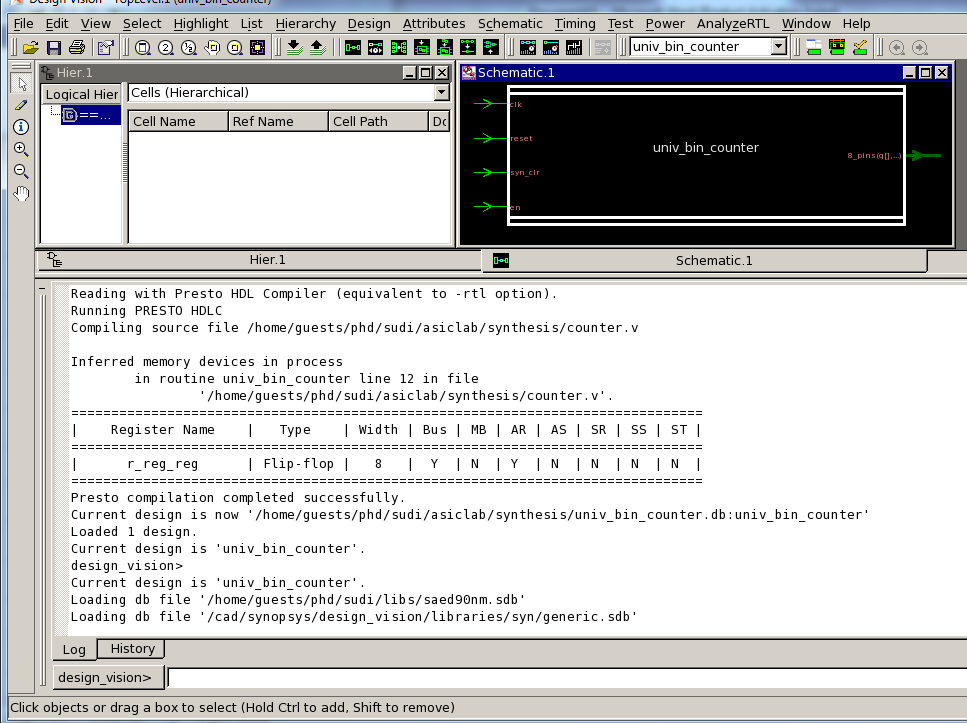

12. Click ok and Read the design (design.v):-

13. Constraints are optional and we can synthesize the design with or without constraints. In this case, we synthesize the design using constraints.

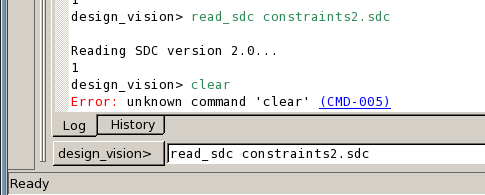

14. Read the constraints using the command: – read_sdc constraints2.sdc (constraints are desiged for counter design).

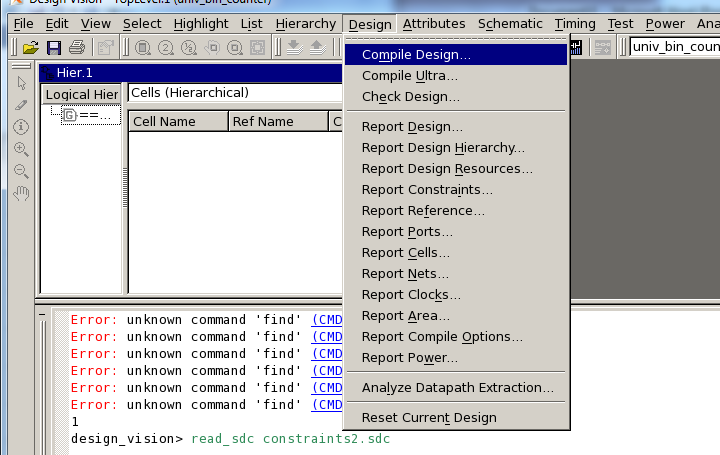

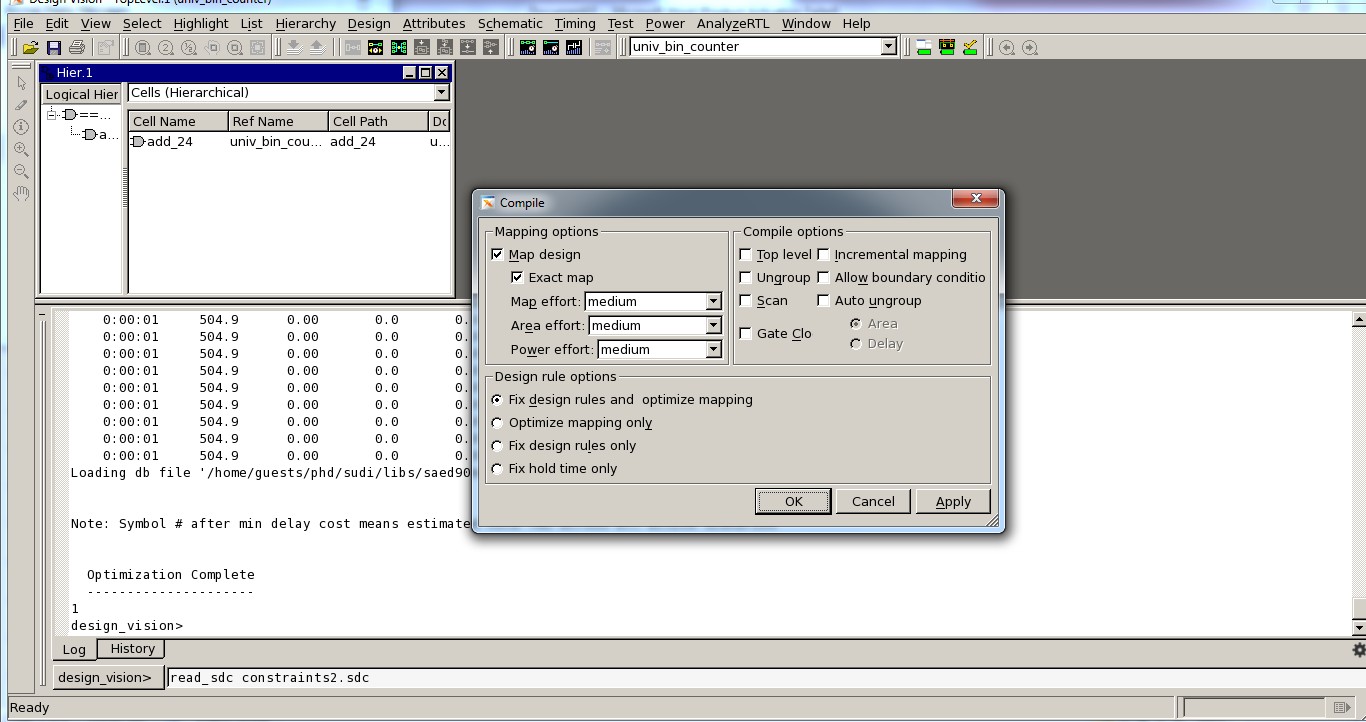

15. Compile design: –

16. Click on OK to compile the design.

17. Execute the following commands: –

report_area.

report_power.

report_timing.

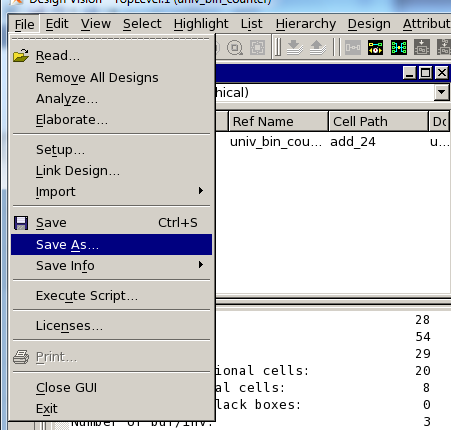

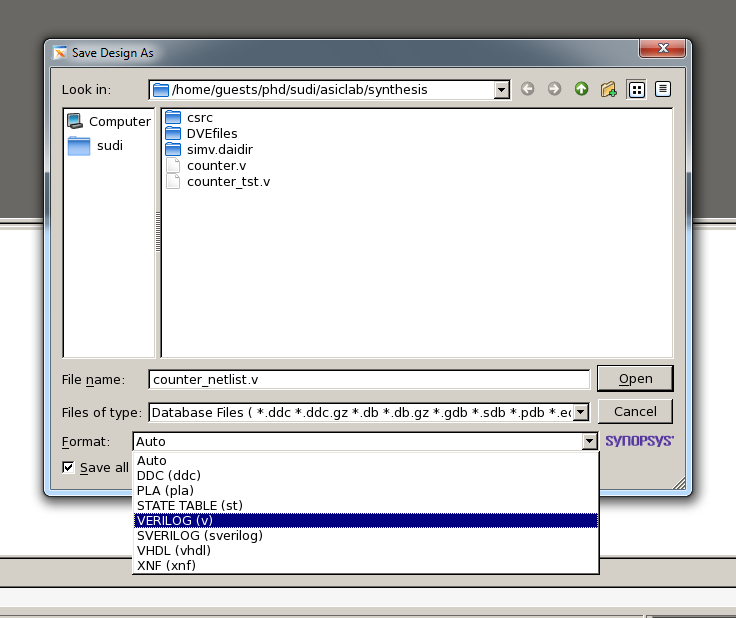

18. Save the gate level netlist for the design (in this case, design is counter.v)

Save the gate level netlist as below: (file name:- counter_netlist.v and format: – change to Verilog ): –

19. File -> exit the design_vision and view the gate level netlist (using gedit command)

20. Simulate the gate level netlist using Synopsys VCS tool as below: –

Post Credit

Faculty Advisor: Prof. Kamalakanta Mahapatra

Instructor: K Sudeendra, Teaching Assistants: S K Ram, J P Mohanty

VLSI Laboratory

The VLSI laboratory at ECE Department of NIT Rourkela is obliged towards the support and encouragement of Ministry of Electronics and Information Technology, Government of India. The overall activities is purely supported by the Special Manpower Development Program for Chips to System Design (SMDP-C2SD) project.