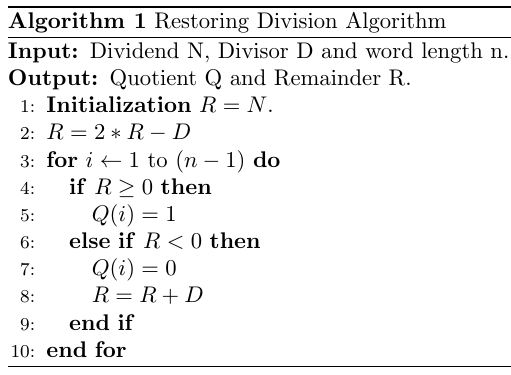

The division operation is carried away by assuming fractional numbers and it is assumed that D and N are positive numbers. The Restoring division algorithm is shown below. Here n is the data width and R is set to N initially.

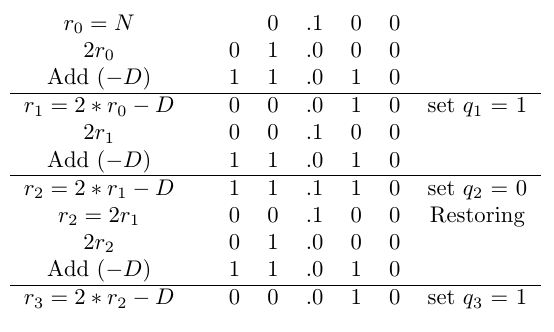

An example of Restoring division is given below. Here N = 0.5 (0.100) and D = 0.75 (0.110). The output Q is 0.625 (0.101). The value of n is 4 here.

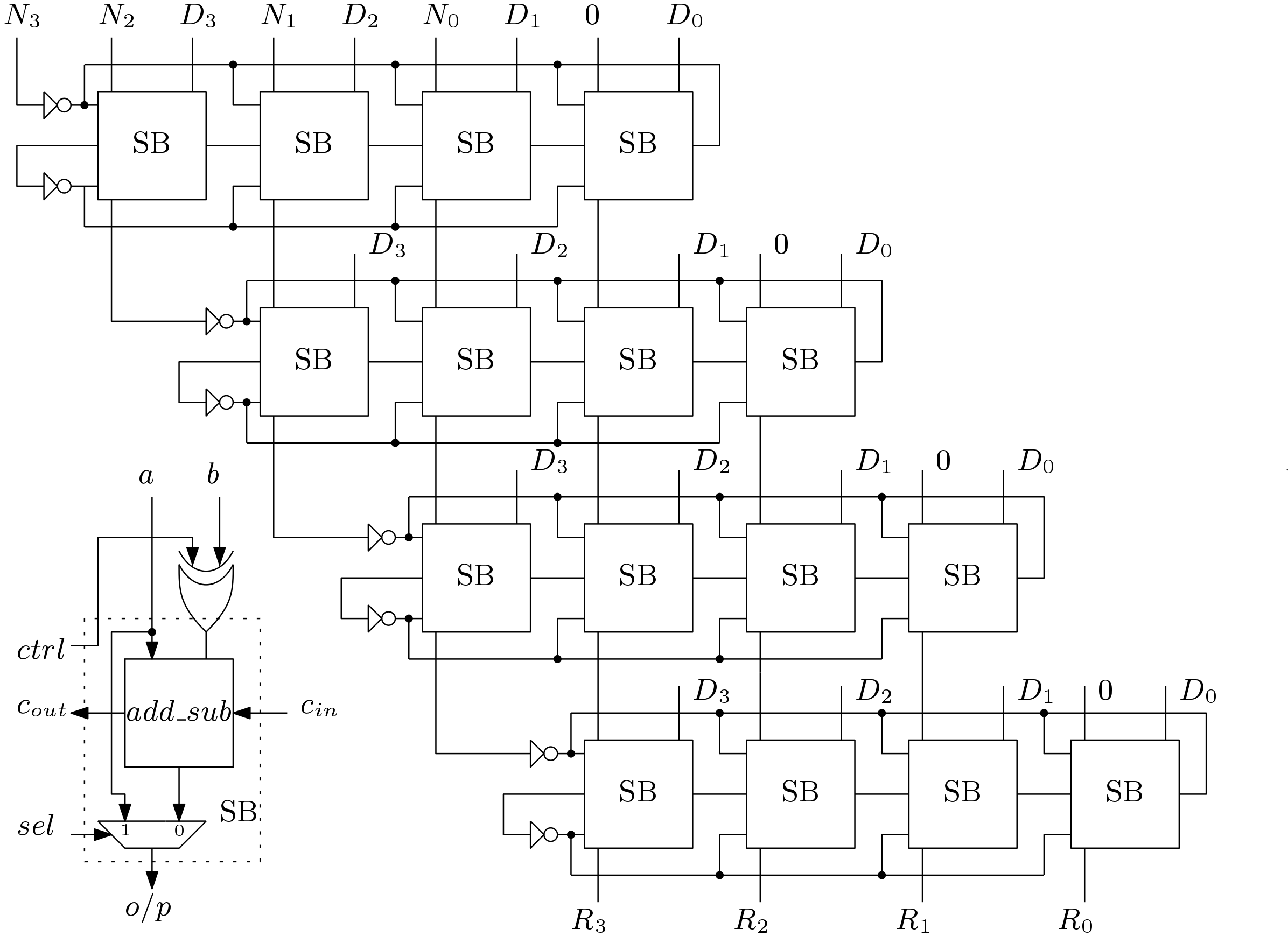

The architecture for Restoring division is shown below. There are two conditions which are checked in Restoring division. One is to check whether r is positive or not and another is when to restore. The basic SB blocks are made of two’s compliment subtraction and controlled output mechanism. The Verilog code of Restoring division is given below.

Click here to download the Verilog code of Restoring division architecture.

very nice publish, i actually love this web site, keep on it!