The Gold-Schmidt division is one of the popular fast division methods. It evaluates the division operation by iterative multiplications. The equations which govern Gold-Schmidt division are

![]()

![]()

![]()

The major advantage of Gold-Schmidt division is its low latency. In VLSI

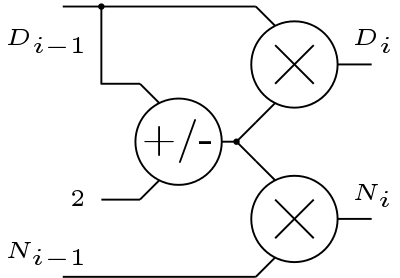

implementation where a designer wants to fasten the design performance then this divider can be used. The block diagram of this divider is shown below in figure 1

It uses two multipliers per iteration. One of the disadvantages of this division is that pipeline implementation is costly. Thus serial implementation is beneficial to use. Another disadvantage of this divider is its accuracy. The need for the pre-scaling of input operands makes it not suitable for systems with high accuracy. More iteration means greater accuracy which again increases cost.

It uses two multipliers per iteration. One of the disadvantages of this division is that pipeline implementation is costly. Thus serial implementation is beneficial to use. Another disadvantage of this divider is its accuracy. The need for the pre-scaling of input operands makes it not suitable for systems with high accuracy. More iteration means greater accuracy which again increases cost.

The Verilog implementation of the pipeline version of Gold-Schmidt division is given below in the link to download. In this implementation 5 iterations are used. We have used 18 bit data width with 9 bit fraction. All the multipliers and adders are implemented by simply writing Verilog commands for simplification.

Click here to download the code.