Automatic Test Pattern Generation and Automatic Test Pattern Generator (ATPGA) is an electronic design automation method/technology used to find an input (or test) sequence that, when applied to a digital circuit, enables automatic test equipment to distinguish between the correct circuit behavior and the faulty circuit behavior caused by defects. This tutorial focuses on ATPG for combinational circuits using Synopsys Tetramax tool.

1. Open the terminal

2. Source the synopsys_tmax.cshrc

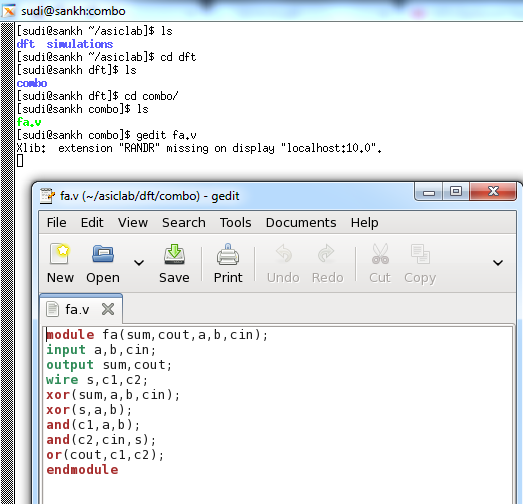

3. In a ASIC lab directory, make design.v (any combinational circuit). In this experiment, we perform ATPG for Combinational Circuits.

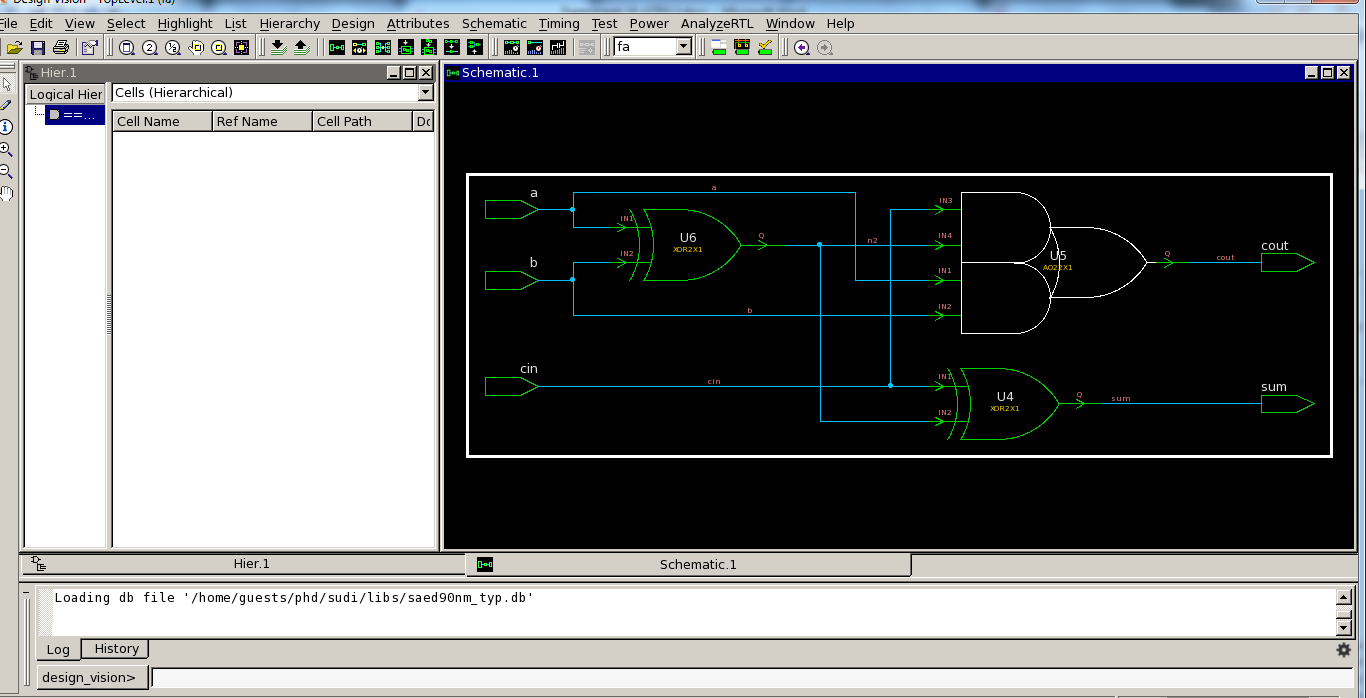

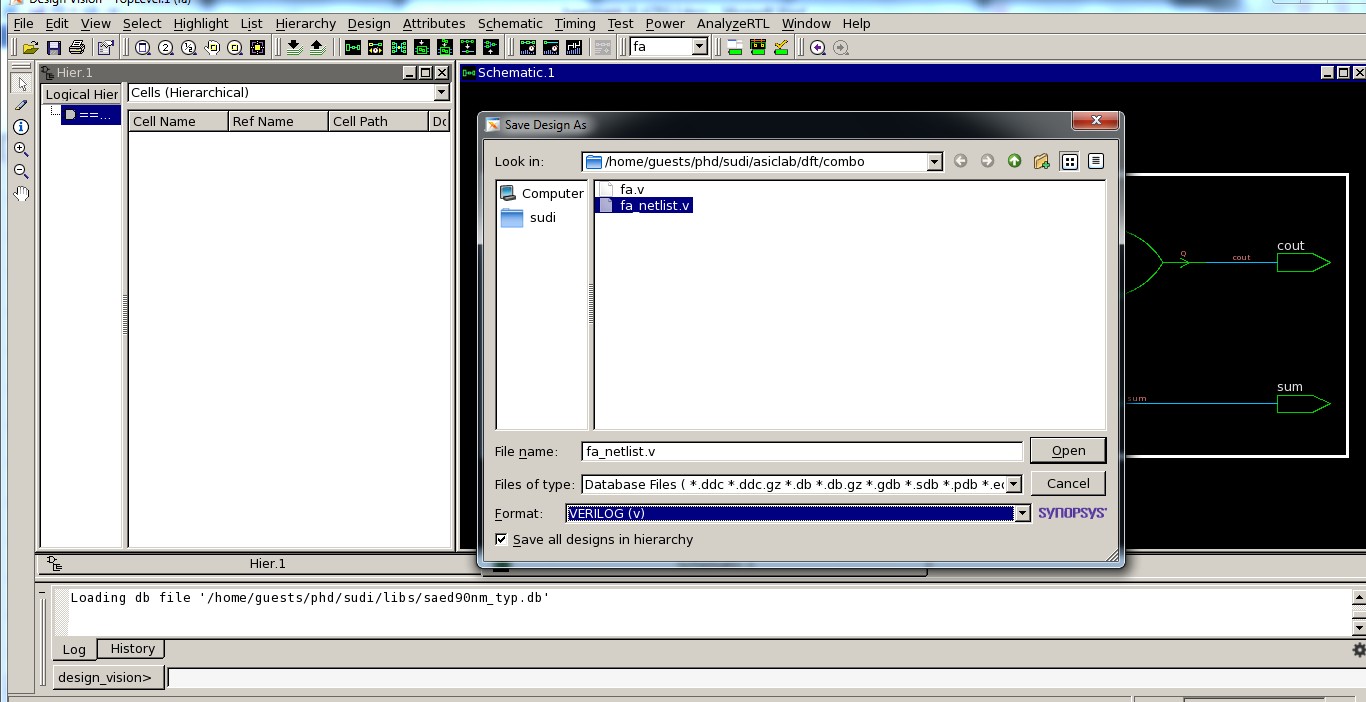

4. Synthesize the combinational circuit in design_vision (without constraints, you can do with constraints also). This is shown in our previous tutorial on synthesis. Follow the steps described in synthesis experiment. Save the netist in verilog format.

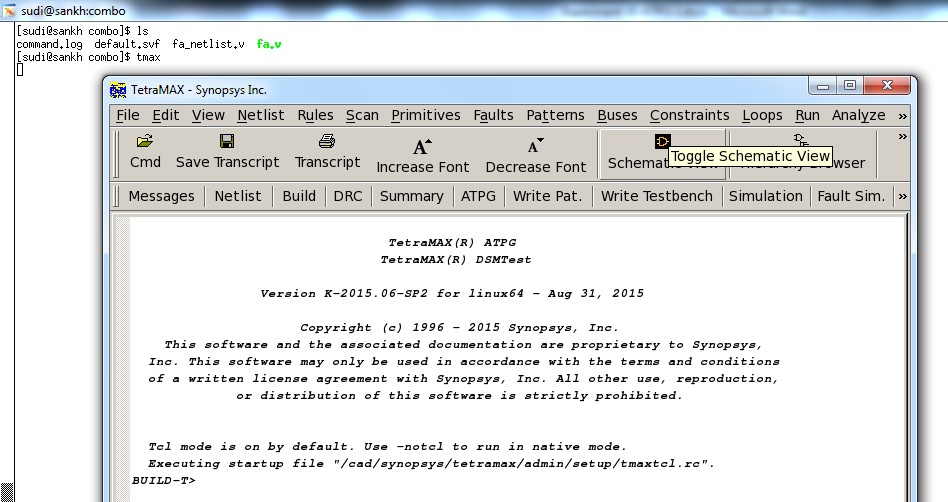

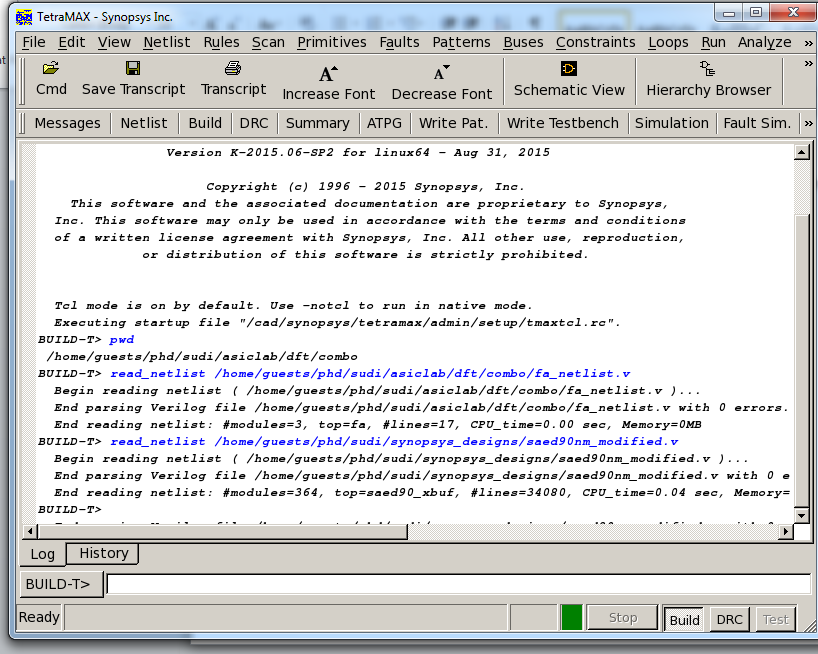

5. Open Tetramax tool (Synopsys ATPG tool)

6. Read design_netlist.v (combinational circuit synthesized in design_vision) and library.v

(saed90n_modified.v). Available in your libs directory.

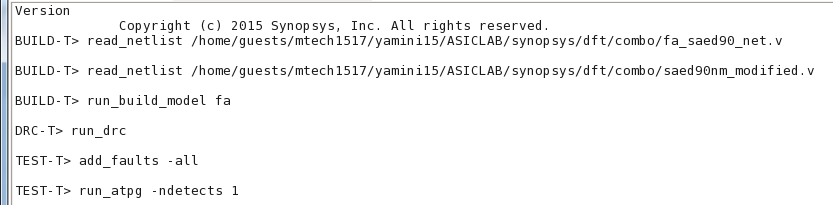

7. Execute the following commands in Tmax command line: –

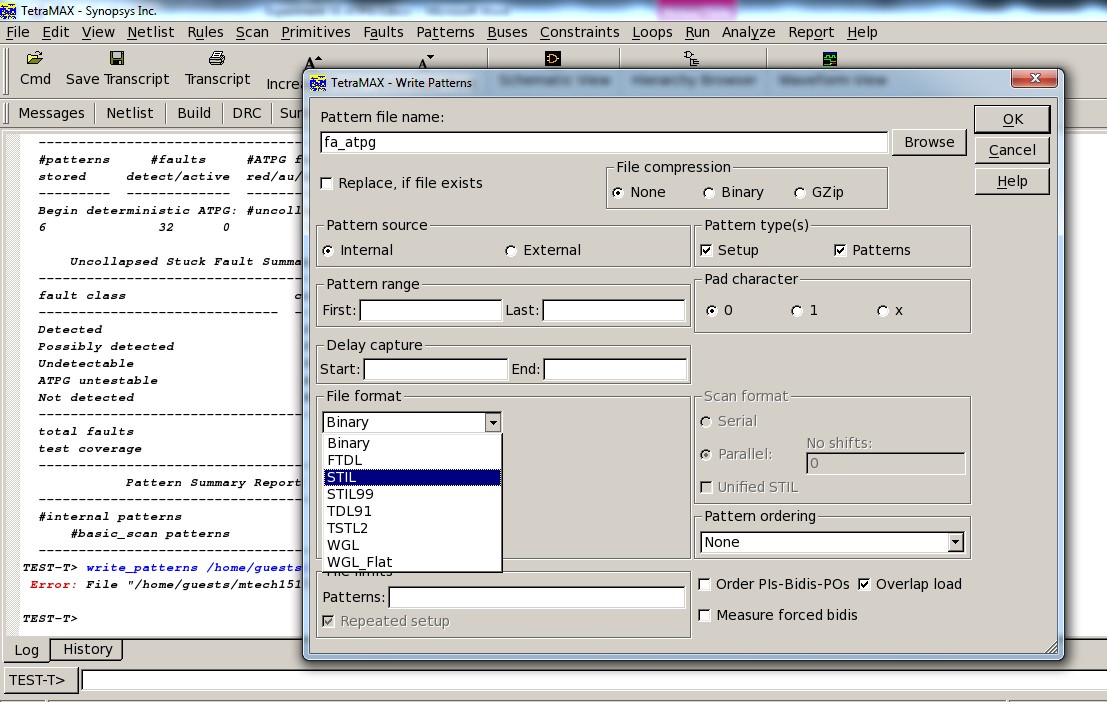

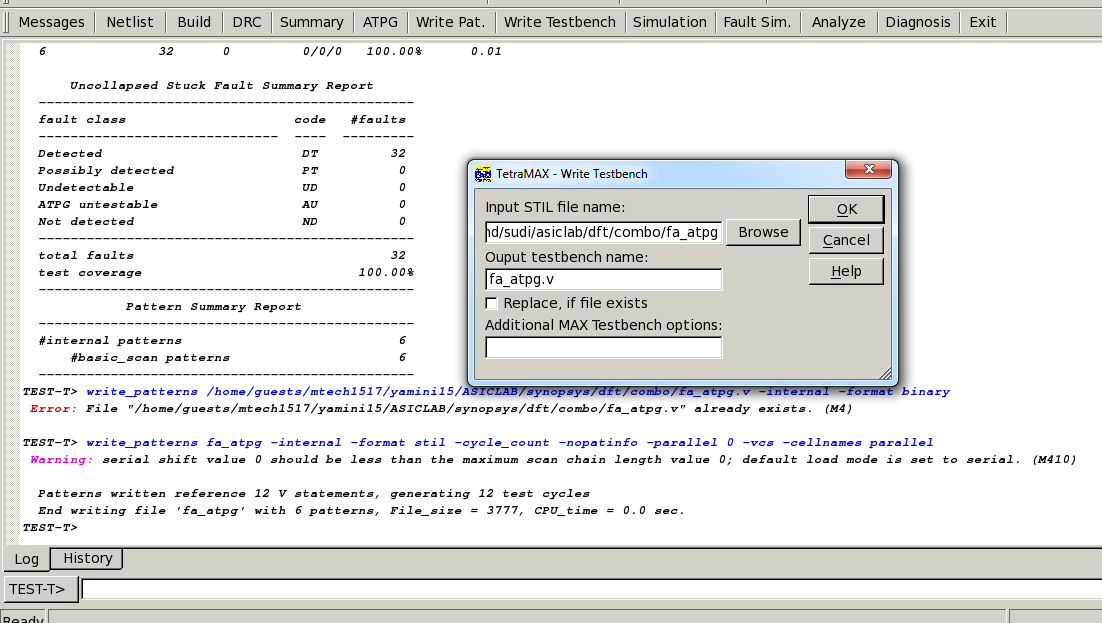

8. Save the patterns in the form of STIL format. (as shown below): – (click on write_patterns to get below window)

9. Click on the Write Testbench on browse on point to fa_atpg file and give a output file name as fa_atpg.v .

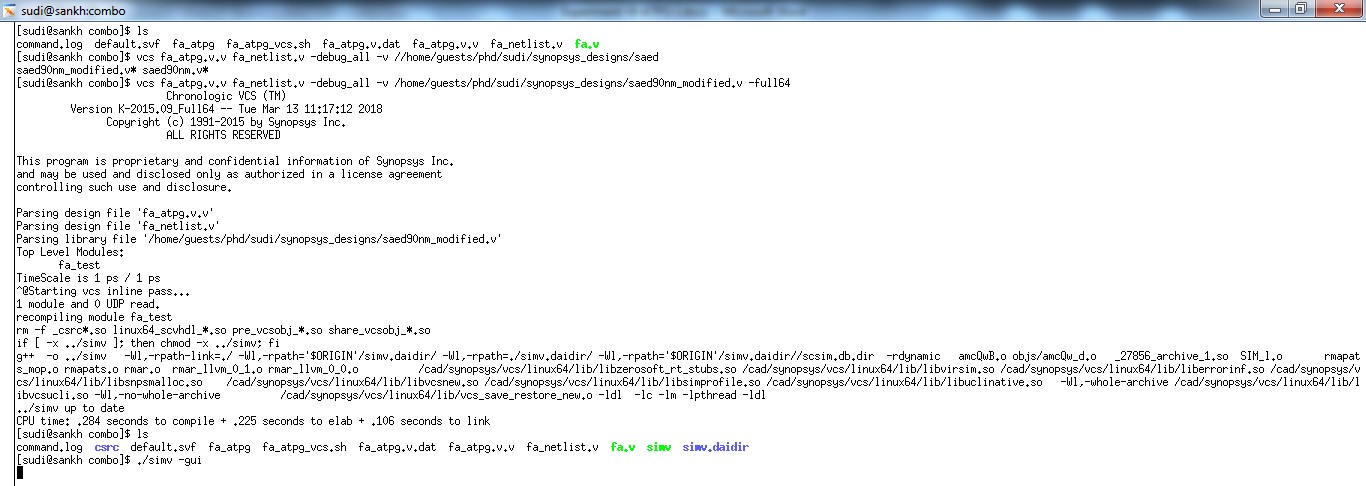

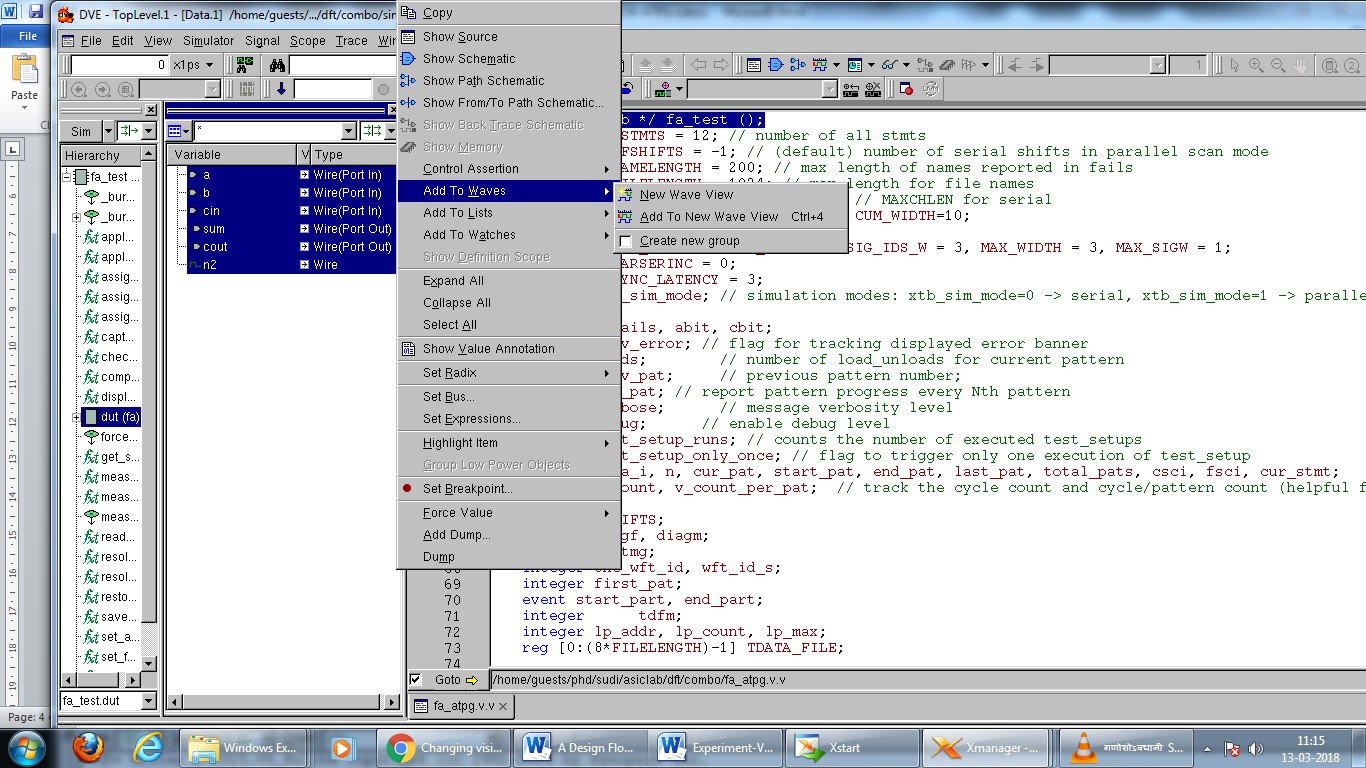

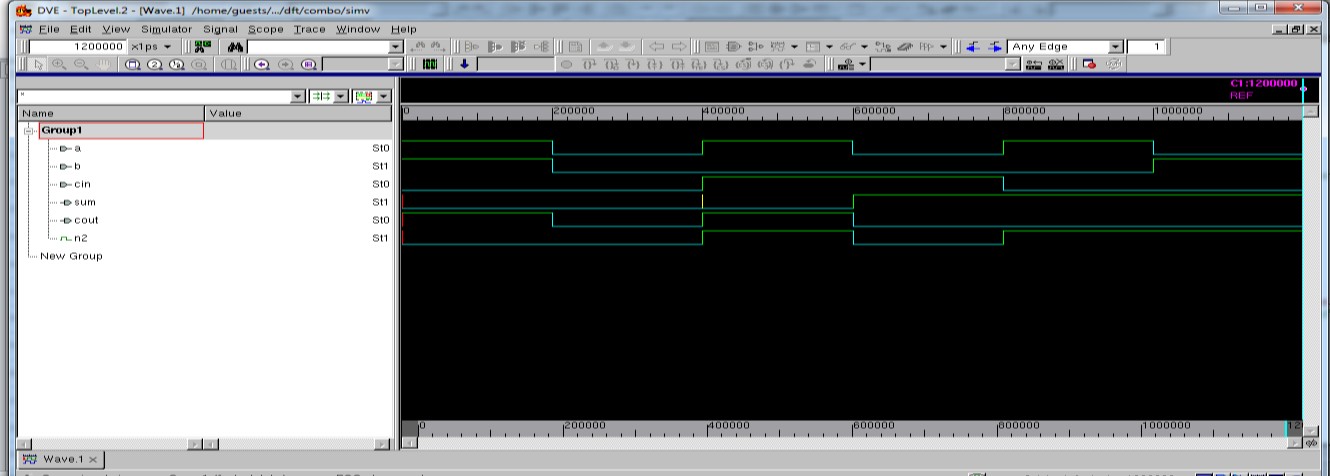

10. Exit Tetramax and Simulate the atpg as below: –

11. Simulate the atpg as below: –

Post Credit

Faculty Advisor: Prof. Kamalakanta Mahapatra

Instructor: K Sudeendra, Teaching Assistants: S K Ram, J P Mohanty

VLSI Laboratory

The VLSI laboratory at ECE Department of NIT Rourkela is obliged towards the support and encouragement of Ministry of Electronics and Information Technology, Government of India. The overall activities is purely supported by the Special Manpower Development Program for Chips to System Design (SMDP-C2SD) project.