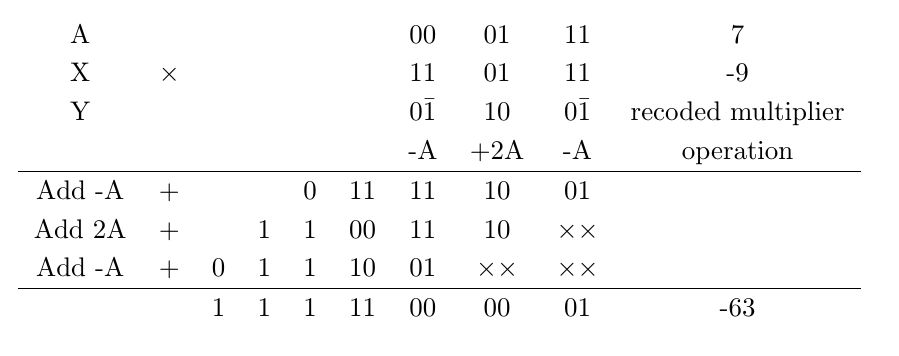

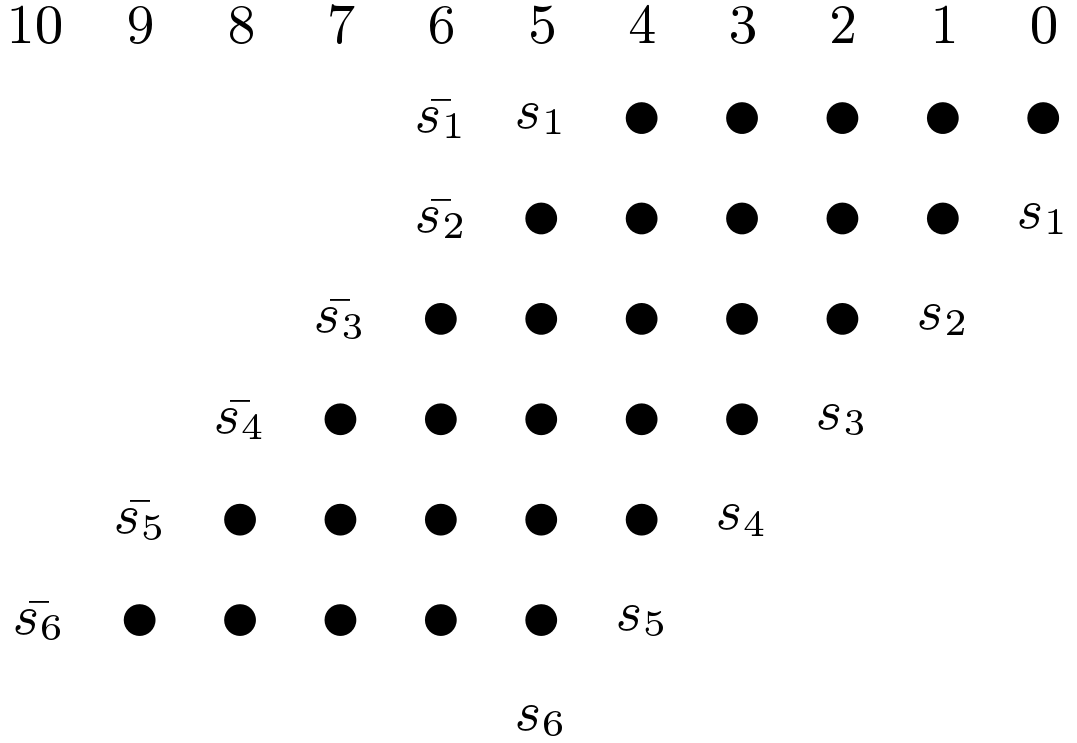

Earlier we have discussed how the partial products for a unsigned multiplier can be accumulated using suitable organization and consuming minimum number of counters. In this section, accumulation will be done by considering negative partial products. If some of the partial products are negative numbers represented in two’s complement number system, then matrix of bits needs to changed. All the sign bits must be properly extended before addition. The extension of sign bit is shown in Figure 1 for 6-bit partial products. Here the filled circles are representing sign bits. This modification increases the hardware complexity and also the number of stages. If the two’s complement numbers are obtained by generating one’s complement then a carry must be added in the least significant bit. This will again increases the hardware complexity.

A six bit partial product ![]() represented in two’s complement can be represented using 11-bit as

represented in two’s complement can be represented using 11-bit as

![]()

whose value is

![]()

can be replaced as

![]()

since

![]()

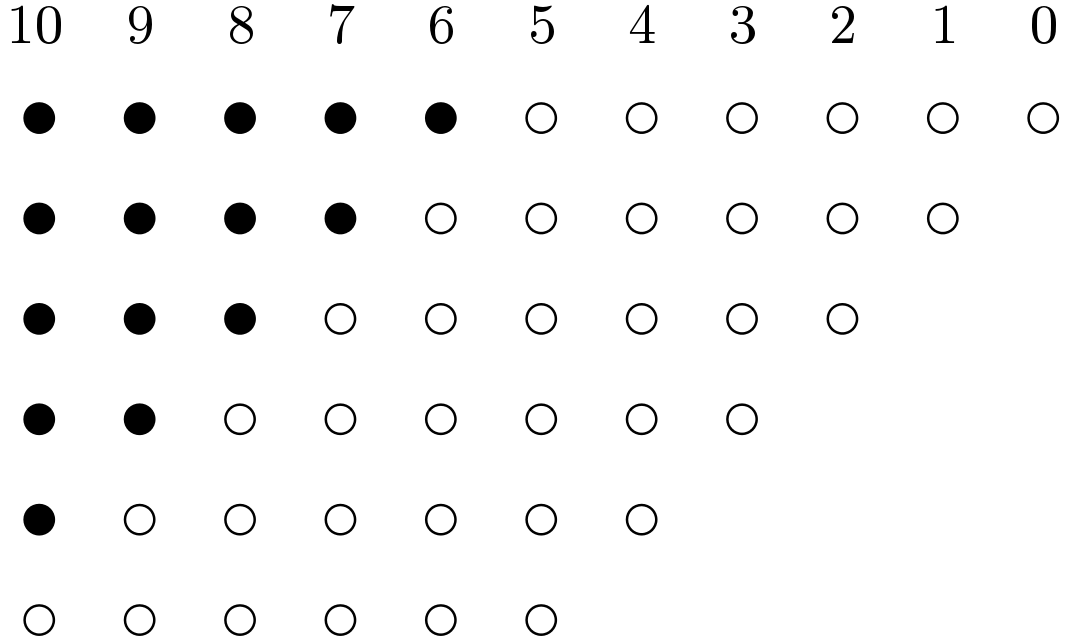

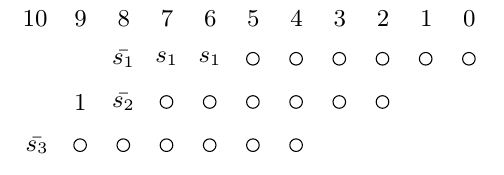

To represent the value -s in column 5, the original sign digit s is complemented to obtain (1-s) and 1 is added. This way we get -s in the column 6 along with a carry of 1. This carry serves as the extra 1 to deal with the sign of the second partial product. This way sign bit of all the partial products are dealt with. This solution is shown in Figure 2. Here number of bits compared to the array in Figure 1 is reduced but the height is increased.

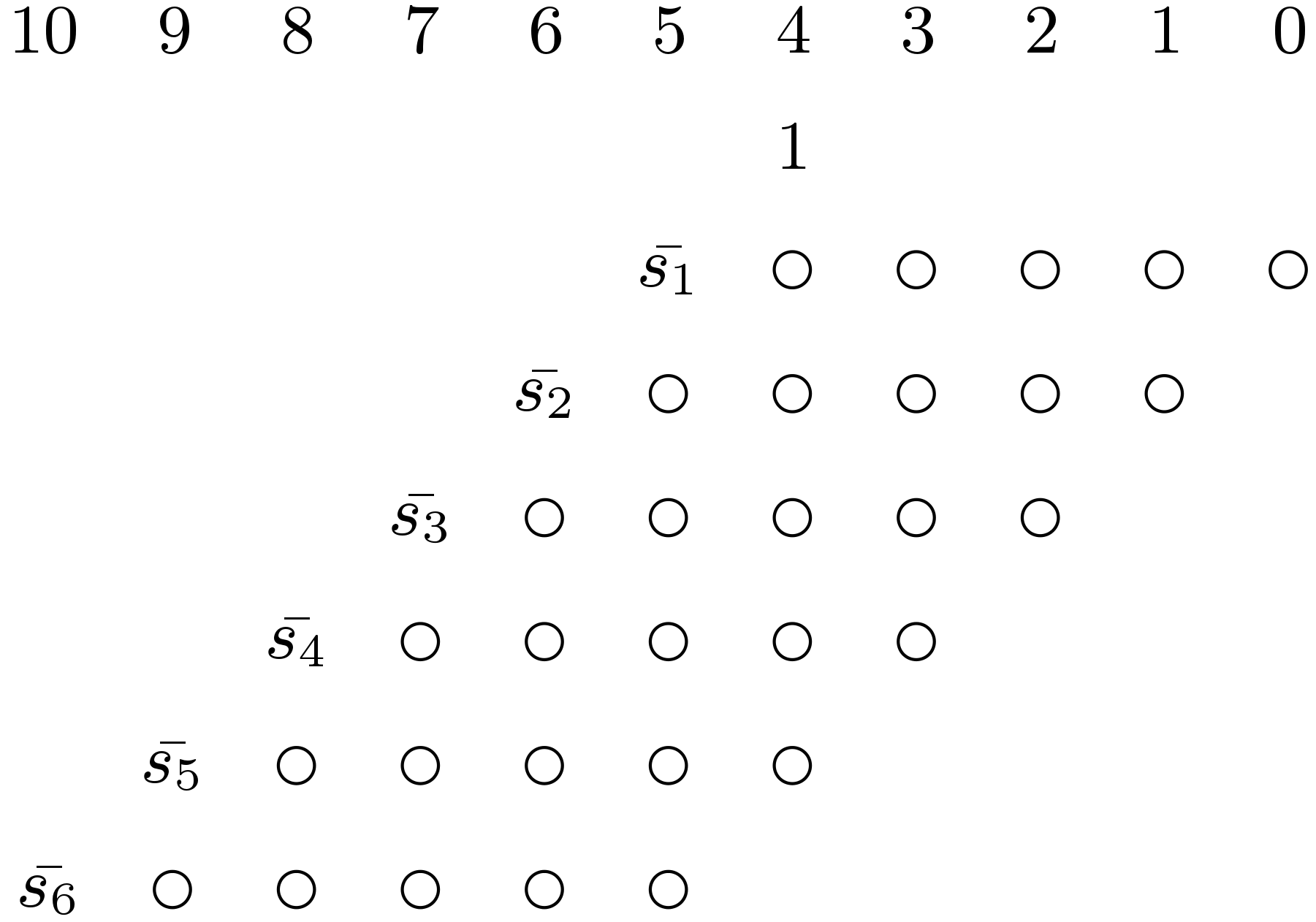

The disadvantage of the first solution is that its length is 7. Now, the 1 in the column 5 can be eliminated if the two sign bits ![]() and

and ![]() can be placed in the same column. This is possible as

can be placed in the same column. This is possible as ![]() . This 2 is carried out to the next column leaving

. This 2 is carried out to the next column leaving ![]() and

and ![]() . The extra 1 in column 5 is no longer required. Placing the two sign bits in the same column is achieved by extending the sign bit

. The extra 1 in column 5 is no longer required. Placing the two sign bits in the same column is achieved by extending the sign bit ![]() bit in one position as shown in Figure 3.

bit in one position as shown in Figure 3.

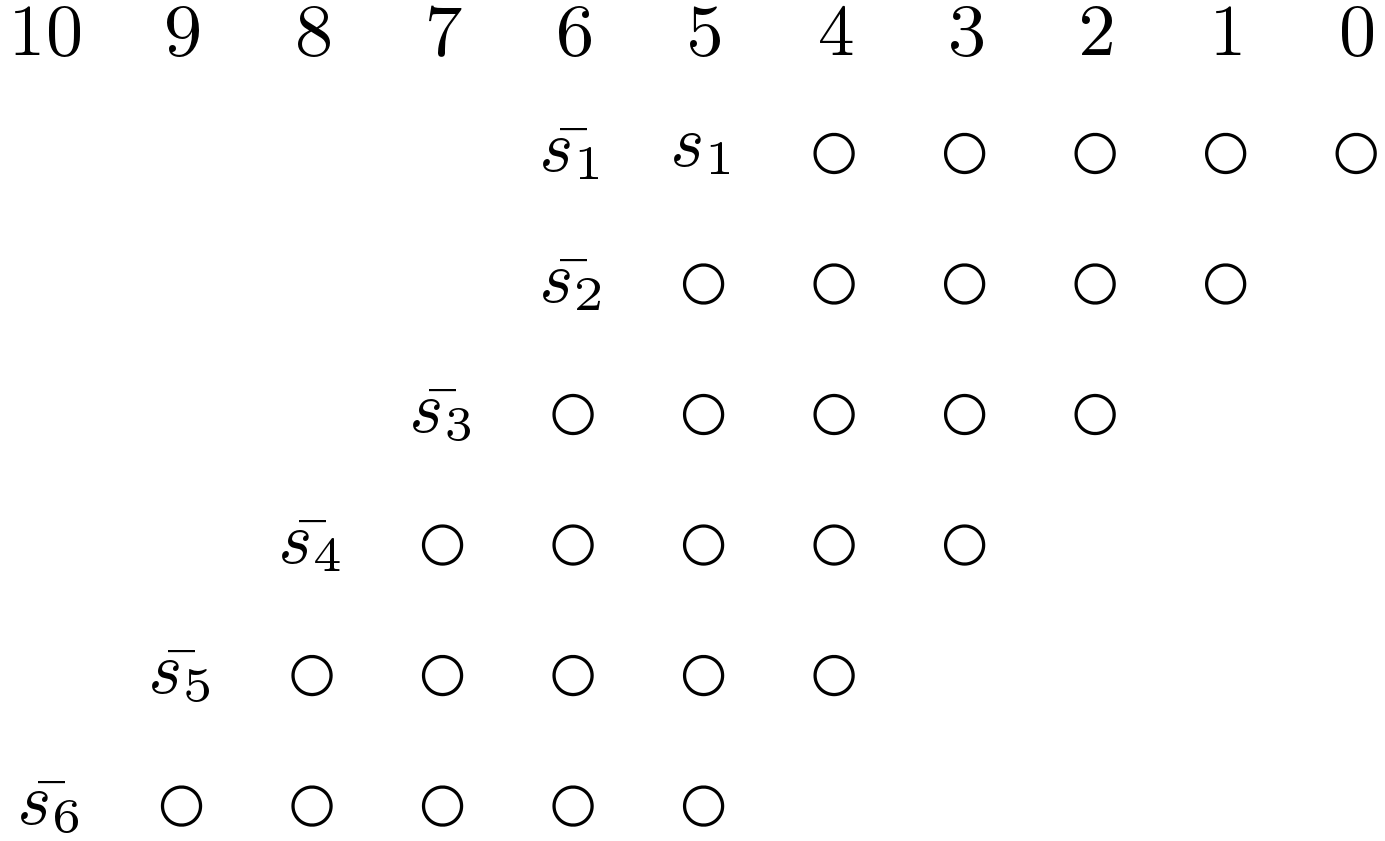

If the negative partial products are obtained by first generating the one’s complement and then adding a carry at the least significant side then the arrangement can be made different. The extra carry at the LSB side is then must be added to the matrix. This solution is shown in Figure 4 where the filled circles represent the complements of the bits whenever ![]() . Here in this solution the height of the matrix is again 7 but for the unsigned case the last carry at the LSB side can be omitted.

. Here in this solution the height of the matrix is again 7 but for the unsigned case the last carry at the LSB side can be omitted.

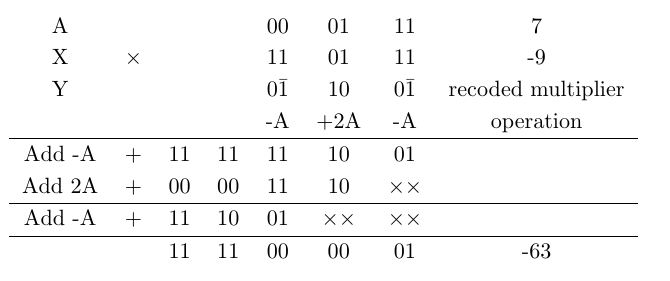

The accumulation of signed partial products can be explained using an example. Let us consider the multiplication of two 6-bit numbers using Booth’s Radix-4 algorithm as used in previous tutorial. The partial products can be written as shown in Table 1.

Here two partial products are negative represented in two’s complement format. The above mentioned techniques can be applied to decrease the number of operands. The general technique to reduce the operands in case of Radix-4 Booth algorithm for signed partial products is shown in Table 2.

The matrix of the operand bits of Table 1 is modified by applying the second technique as shown in Table 3.