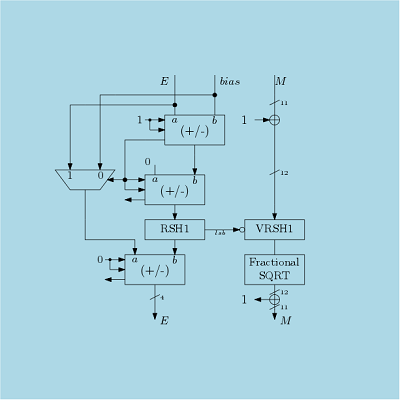

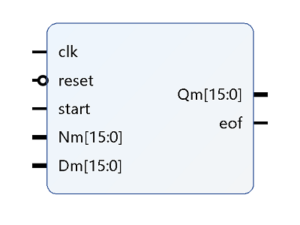

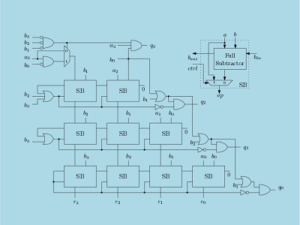

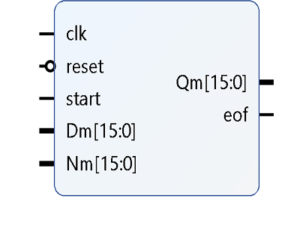

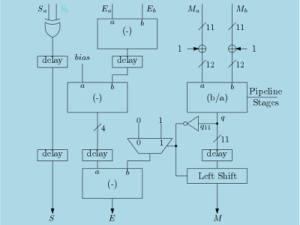

Design and implementation of square root block is as difficult as it is difficult to design a divider block. Here Verilog Code for 11-bit Floating Point Parallel Square Root Block is provided. Here, 1-bit is used to represent sign, 4-bits are used to represent the biased exponent and 6-bits are used for the magnitude part. This block is a parallel design and the fixed point square root is Non-restoring algorithm based.

Arithmetic Blocks

Verilog Code for 11-bit Floating Point Parallel Square Root Block

$2.50

Specifications

- Floating Point Parallel Square Root Block.

- Word Length – 11-bits

- Square Root Block – Non-restoring algorithm based.

- 1-bit for sign, 4-bits for exponent and 6-bits for magnitude.

- Verified at simulation level only.

- Structural Verilog design based.

Manoj –

Best topic