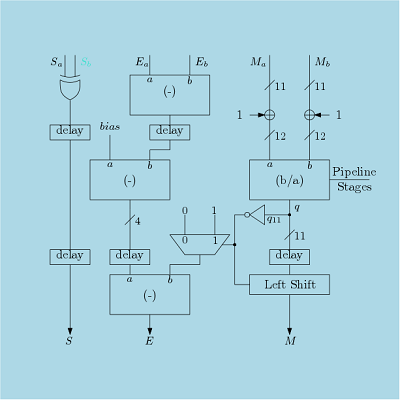

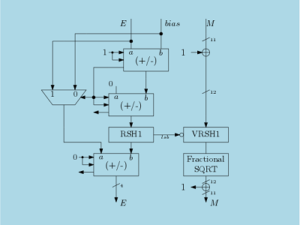

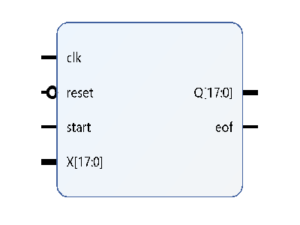

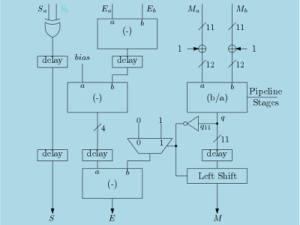

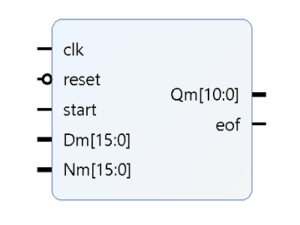

Divider is a very complex digital block to design and it consumes more hardware resources than the other arithmetic blocks. Now the implementation of divider block in floating point representation is even more critical. Here, a Verilog implementation of 16-bit floating point divider is presented. Here, 16-bit frame length is used to represent the floating point representation. Out of which 11-bits are used for magnitude part and 4-bits are used for biased exponent. Remaining 1-bit indicates the sign of the number. The divider is parallel and pipeline stages are inserted to achieve higher frequency of operation.

Arithmetic Blocks

Verilog Code for 16-bit Floating Point Pipelined Divider

$4.00

Product Specifications

- 16-bit Floating Point Divider

- Parallel and Pipelined

- 4-bits for Biased Exponent and 11-bits for Magnitude

- Structural Verilog Design

- Fixed point divider is 18-bit unsigned.

- Result is verified by simulation. FPGA implementation is not verified.

Reviews

There are no reviews yet.