Divider is very important block in digital system design and this block has the highest complexity than other arithmetic blocks. Thus it is best practice to avoid it if possible. But most critical signal processing algorithms can not avoid it and thus should be implemented on hardware. We have designed a Fixed Point Signed Divider IP which can receive inputs of any size and evaluation division operation.

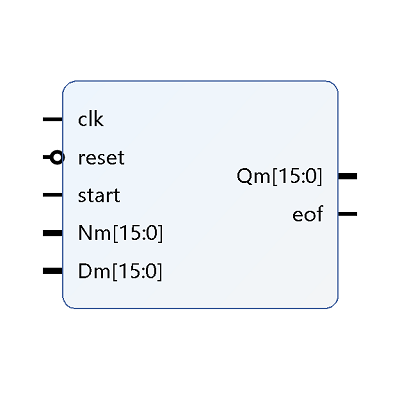

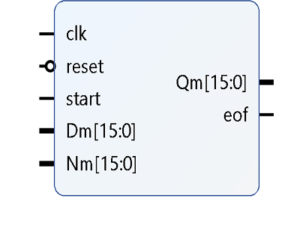

This IP has five inputs clk, reset, start, numerator (Nm) and denominator (Dm). It has two outputs , Quotient (Qm) and eof. The signal start is aligned with the input data so that the signal eof can track the output. Three parameters are needed to be set which are N, M and sign. N indicates the data width, M indicates the precision, and sign indicates whether the IP is used for signed division or unsigned division. If sign is 1 then signed division and if sign = 0 then it is for unsigned division.

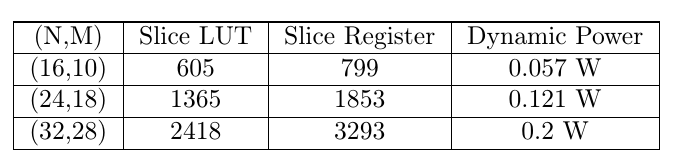

Fixed Point Signed Divider IP is implemented on Xilinx XC7A35T-1FTG256 Artix 7 FPGA for different parameters. Frequency and power analysis have been carried out. FPGA performance is measured at 200 MHz although more than this frequency can be achievable. Its FPGA performance is shown below.

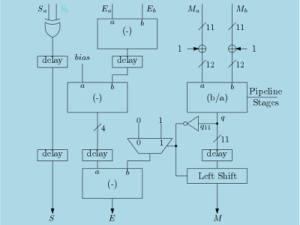

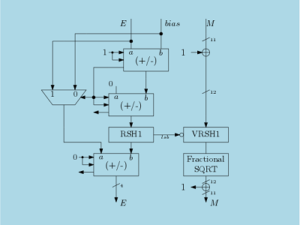

Fixed Point Signed Divider IP is designed with Verilog HDL and verified with ILA using Vivado 2019.1. This IP is fully parallel and pipelined. This IP has latency of (N+M) clock cycles when unsigned division option is chosen and this IP has latency of (N+M+2) clock cycles when signed division is done.

Reviews

There are no reviews yet.