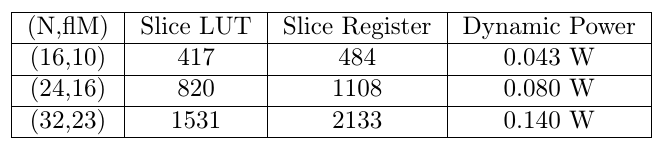

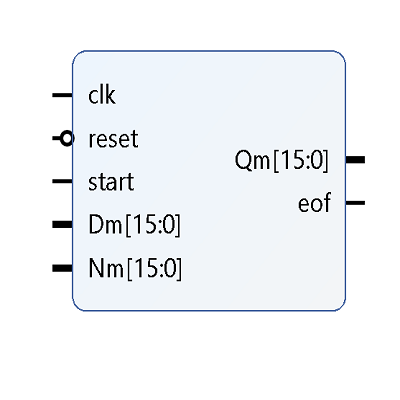

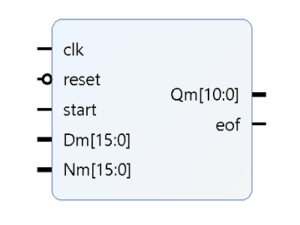

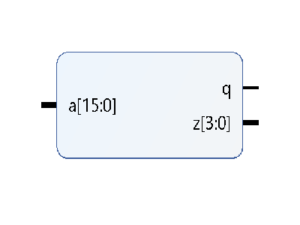

Floating point divider IP is another critical block in digital system design just like floating point square root block. We have made a simple general floating divider IP which can be used for rapid prototyping a FPGA implementation. This IP has two customization parameters which are N (data width) and flM (width of the mantissa). In this product we have considered the IEEE standard format of representing the floating point numbers where hidden bit is not considered. Furthermore we are considering only normalized numbers. This block uses a simple fixed point divider to achieve the mantissa division and this fixed point divider is non-restoring algorithm based. This IP is fully tested and implemented on Xilinx XC7A35T-1FTG256 Artix 7 FPGA. FPGA performance is shown below.

Dynamic power is calculated at 200 MHz although this IP is capable to work at higher than this frequency. This IP has latency of (2*flM + 3) number of clock cycles. This is a fully parallel and pipelined signed divider IP.

Reviews

There are no reviews yet.