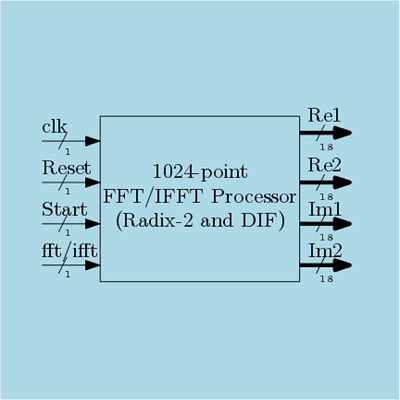

Fast Fourier transform (FFT), an efficient technique to perform discrete Fourier transform (DFT), is the most important block in the signal processing domain. FFT is used to convert a signal in time domain to its frequency domain. On the other hand, inverse FFT (IFFT) block is used to convert the signal in frequency domain to time domain. The evaluation technique of FFT and IFFT is very similar and thus it is required to perform both the operations by a single processor. Here, a Verilog Code of 1024-point FFT/IFFT Processor which hardware efficient.

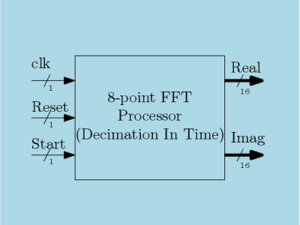

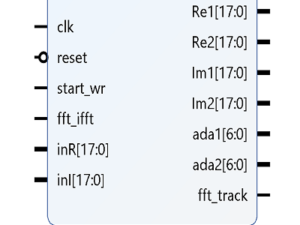

In our previous work, 8-point FFT architecture was implemented. In this work, a 1024-point FFT/IFFT processor is designed. This processor is designed such a way that it can perform FFT and IFFT based on a control signal . This processor is based on Radix-2 decimation in frequency (DIF) technique to implement FFT algorithm. In this design, the input samples are in order but the output samples are not in order.

In an N-point FFT block, n is used to represent the number of stages where . In case of 1024-point FFT/IFFT there will be total 10 stages. In this work, a fully parallel and also pipelined design for 1024-point FFT/IFFT processor is presented. This processor is hardware efficient, fast and also storage efficient.

In this work, a 1024-point FFT/IFFT processor is designed and this processor performs both FFT and IFFT based on a control signal. Performance analysis is carried out here in terms of hardware, speed and power consumption. Total latency of this processor for is (1023 + 10) = 1033 clock cycles.

Hardware complexity is another parameter which is also should be analyzed to measure the performance of this processor. The Verilog implementation of the processor is targeted to the XC7A100T-2CSG324 FPGA module. The architecture is designed and validated using 18-bit fixed representation, where 8-bits are used for integer part and 10-bits are used for fractional part.

Reviews

There are no reviews yet.