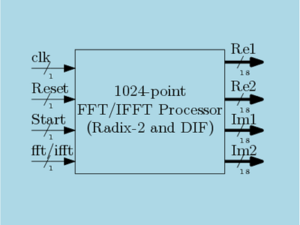

FFT/IFFT processor block is probably the most important DSP block which is used in many complex signal processing systems. Thus it is very important to develop an IP for this block which supports variable data width and variable size of length. This product is a Parallel and Pipelined LUT Based FFT/IFFT Processor IP which supports variable data width and variable length of FFT. This block is well suitable for moderate to high frequency operations.

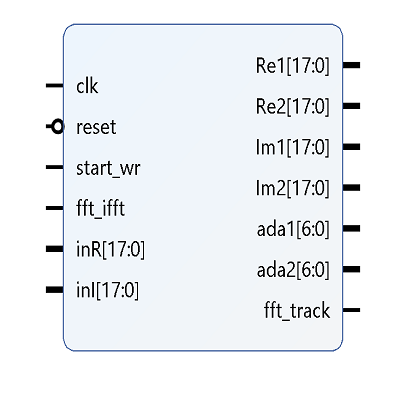

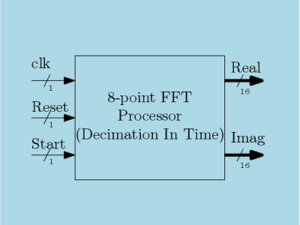

This IP has three parameters which are N = Data width, FrN = Precision and M. The parameter M is used to represent the FFT length. The FFT length is expressed as ![]() . This means for FFT length of 1024, value of M is 10. Apart from clock and reset this block has 4 inputs and 7 outputs. start_wr is a start pulse which start the FFT/IFFT operation. The fft/iift signal whether FFT operation is carried away or IFFT operation. If this signal is 1 then FFT operation is performed. The FFT/IFFT Processor IP receives external imaginary inputs through inR and inI inputs.

. This means for FFT length of 1024, value of M is 10. Apart from clock and reset this block has 4 inputs and 7 outputs. start_wr is a start pulse which start the FFT/IFFT operation. The fft/iift signal whether FFT operation is carried away or IFFT operation. If this signal is 1 then FFT operation is performed. The FFT/IFFT Processor IP receives external imaginary inputs through inR and inI inputs.

FFT/IFFT Processor IP has throughput of two. Means it can produce two complex outputs per clock cycle. These outputs are Re1, Re2, Im1 and Im2. The ada1 and ada2 denotes the addresses which actually locates the outputs. This is for if the inputs are applied in right order. If the inputs are given in the reverse order then they invaluable. But if the inputs are given in right order then they show the reverse addresses to help the user to understand the output values.

FFT/IFFT Processor IP supports FFT length from 32 to 8192. FFT length should be power of two. This processor also supports any data width but maximum precision it supports is 30 bits. This is a LUT based processor thus all the constants are stored in LUTs which are visible to the end user. This processor has very high accuracy as it is LUT based. Accuracy is measured in terms of RMSE which is found order of 0.0020.

FFT/IFFT Processor IP is fully parallel and pipelined thus it achieves high frequency. This processor is also memory efficient. This processor takes time (in terms of clock cycles) which is nearly equal to the length of FFT. This processor is very much suitable for windowed FFT/IFFT operations. Performance report of this block is given below

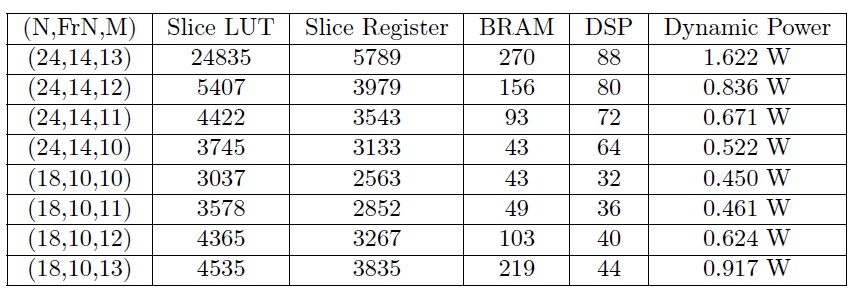

This FFT/IFFT Processor IP is fully verified on FPGA. For performance analysis XC7A100tCSG324-2 FPGA target was chosen. In the above table, performance of both 24-bit architecture and 18-bit architecture is shown. In case of 24-bit architecture, dynamic power is calculated at 6 ns clock period and for 18-bit architecture dynamic power is calculated at 5.5 ns.

Conclusion: This architecture is very much suitable for low to moderate frequency operations is 24-bit data width is used. But if 18-bit architecture is used then this architecture can be used in high frequency architectures also.

Reviews

There are no reviews yet.