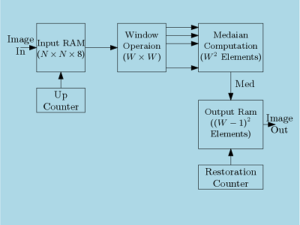

In order to perform image processing, we need to form an window of size ![]() . This window slides from left to right and from top to bottom of an image. We perform on the pixel which is at the center of the window. Thus size of window is always odd. Example are

. This window slides from left to right and from top to bottom of an image. We perform on the pixel which is at the center of the window. Thus size of window is always odd. Example are ![]() ,

, ![]() ,

, ![]() etc.

etc.

Why we need an IP like this? We need to use such IP as many times we need to vary the window size to check the performance of any image processing algorithm. We are offering an IP which is capable to perform window operation of any size and can accept any data width. This IP is a low cost solution of window formation.

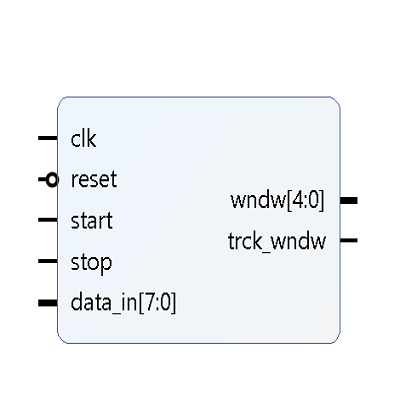

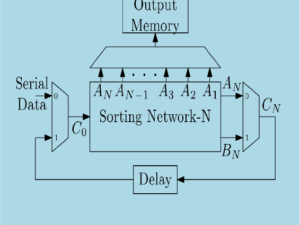

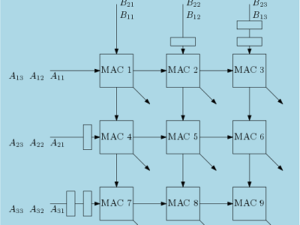

This IP has four parameters which are, N (data width), M (window size), L (Number of bits to represent M-1), and P (size of the row of the image). For example, lets consider we have an gray scale image of size ![]() and we want to apply

and we want to apply ![]() window on it. Then N = 8, M = 3, L = 1, and P = 10. This IP has input control signals like clk, reset, start, and stop. Start pulse needed to be asserted just only clock cycle before the data stream and stop pulse is synced with the last pixel of the image. Output of this IP is an

window on it. Then N = 8, M = 3, L = 1, and P = 10. This IP has input control signals like clk, reset, start, and stop. Start pulse needed to be asserted just only clock cycle before the data stream and stop pulse is synced with the last pixel of the image. Output of this IP is an ![]() image. The output

image. The output ![]() is an two dimensional array of size

is an two dimensional array of size ![]() and each data of this array is of N-bit width. Windows are tracked with the signal

and each data of this array is of N-bit width. Windows are tracked with the signal ![]() .

.

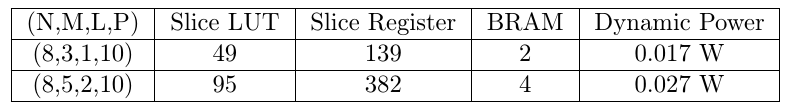

Size of the window can be varied, data width can be varied and this IP can be applied to any image size. This IP is designed with system Verilog and verified by implementing it on Xilinx XC7A35T-1FTG256 Artix 7 FPGA and verified by Vivado logic analyzer. FPGA performance is shown below in a table

The dynamic power of this IP is measured at 200 MHz though more than this frequency is achievable.

Reviews

There are no reviews yet.