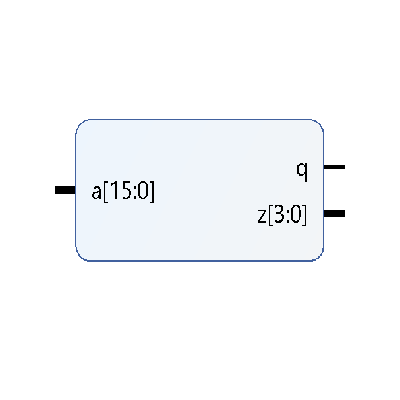

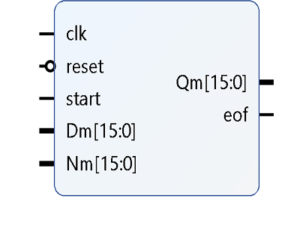

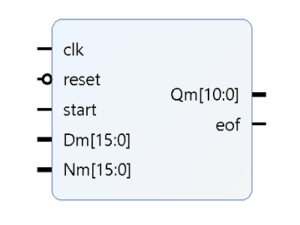

Counting leading zeros is an important operation in many digital systems. This block is also very important in developing floating point arithmetic blocks. Thus we have made this block as an IP so that it helps the researchers in designing complex blocks. General Leading Zeros Counter IP is made such a way that it can count leading zeros of a data of maximum width of 64. This means this block supports maximum N = 64. This block has another parameter p which denotes the data width of zeros count (z). For examples if data width is 16 then value p will be 4. Maximum value of p is 6 for maximum value of N=64. Another important criteria of this block is that data width can be increased by 2 not by 1. For example, we can give data width as 10, 12, 14 etc. Means this block supports only even data width. This block has another output which is q. If q is logic 1 then all the bits of data (a) are zeros. In this case, value of z is invalid.

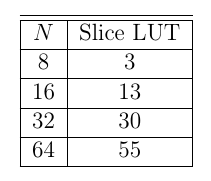

This is initially implemented on Xilinx XC7A35T-1FTG256 Artix 7 FPGA but is supported to any other board. This IP is completely combinational and thus user have to find its detail timing analysis. Resource utilization details is shown below

In order to test the IP, we have used seven segment display to show the zero count. Note that this IP is not tested within a complex design thus frequency performance is not determined.

Reviews

There are no reviews yet.