A discrete cosine transform (DCT) expresses a finite sequence of data points in terms of a sum of cosine functions oscillating at different frequencies. DCT is used in many applications of signal processing like image compression, feature extraction etc. Thus, implementation of DCT is very important in hardware. This product is about LUT based FPGA implementation of 256-point DCT.

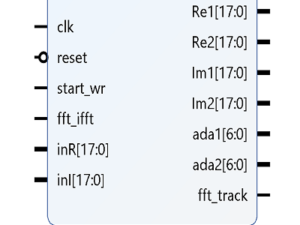

This architecture is fully parallel and pipelined and it uses 24-bit data width. In order to increase accuracy of the architecture, 14-bit precision is used. The constants are LUT based so that high accuracy can be achieved at the cost of few extra memory elements. It has two output signals which are dct_track and dct_end. One signal is used to track the DCT outputs and another indicates that DCT operation is ended.

This implementation is verified by implementing it on xc7a100tcsg324-2 FPGA board and its performance details is

Maximum frequency – 200 MHz, Dynamic Power – 0.358 W

Slice LUT – 2791, Slice Register – 2250, RAM18E – 25, DSP Blocks – 56

This architecture is fully scalable and can be customized as per user requirement.

Reviews

There are no reviews yet.