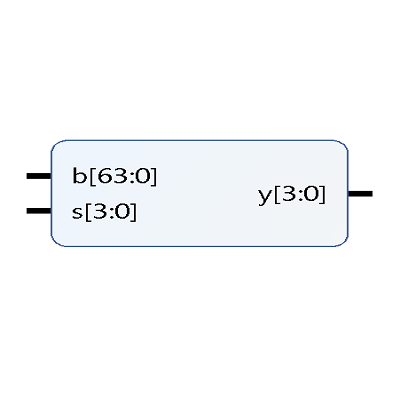

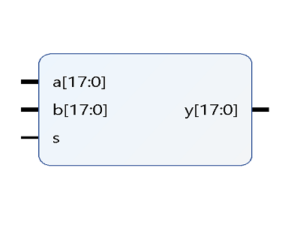

Sometimes in complex digital design we need M:1 multiplexer and the value of M can be anything depending on the requirement of the design. Generally M is chosen as power of 2 and M is represented as ![]() . Here, a general multiplexer IP is designed where both data width (N) and the value of M can be changed. This type of IP gives designer flexibility to easily prototype their complex design. It is suggested that the value of M is chosen as power 2 and put zeros if any input is not required. This IP is designed using Verilog HDL and verified. This is an combinational circuit and if pipeline registers are required then the user is instructed to design smaller multiplexer units and then connect them through registers.

. Here, a general multiplexer IP is designed where both data width (N) and the value of M can be changed. This type of IP gives designer flexibility to easily prototype their complex design. It is suggested that the value of M is chosen as power 2 and put zeros if any input is not required. This IP is designed using Verilog HDL and verified. This is an combinational circuit and if pipeline registers are required then the user is instructed to design smaller multiplexer units and then connect them through registers.

Uncategorised

General N-bit M:1 Multiplexer IP

$2.00

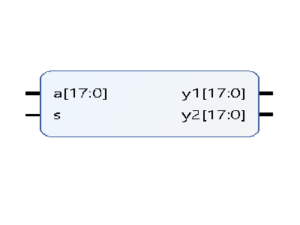

Sometimes in complex digital design we need M:1 multiplexer and the value of M can be anything depending on the requirement of the design. Generally M is chosen as power of 2 and M is represented as $M = 2^p$. Here, a general multiplexer IP is designed where both data width (N) and the value of M can be changed. This type of IP gives designer flexibility to easily prototype their complex design. It is suggested that the value of M is chosen as power 2 and put zeros if any input is not required. This IP is designed using Verilog HDL and verified.

Reviews

There are no reviews yet.