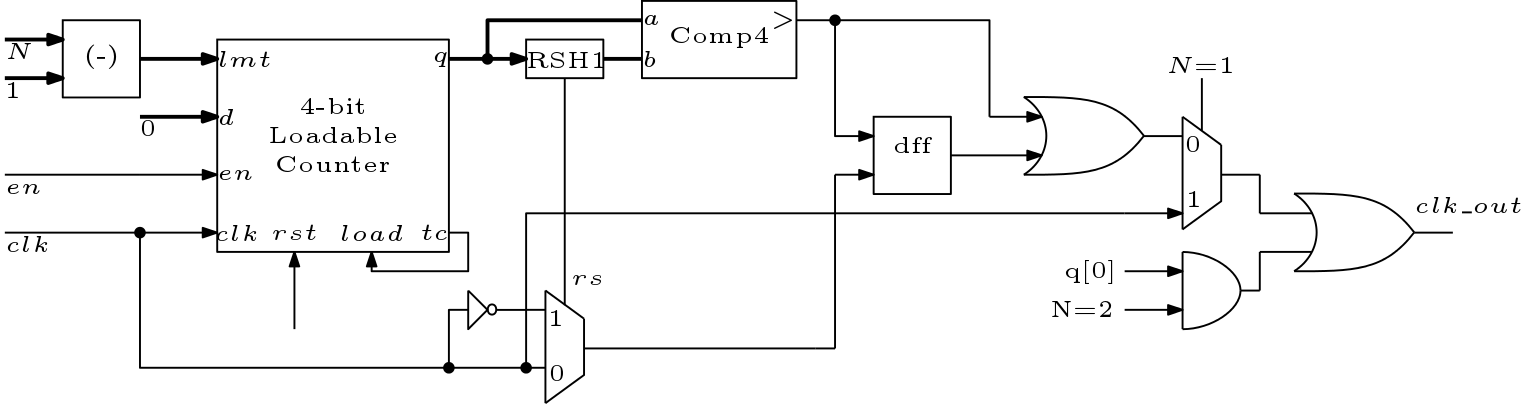

In our previous tutorial sequential circuits, many different clock divider circuits are introduced. Here in this tutorial, a basic architecture of a programmable clock divider is presented. Clock divider circuits have many use in frequency synthesizers. A basic circuit is presented below in Figure 1.

The circuit is capable of dividing the input clock by N where N can take values from 1 to 15. The circuit passes the same input to the output when N = 1. The circuit is based on a 4-bit loadable counter and a 4-bit comparator. The value of N is decremented and passed to the ![]() input of the loadable counter. This increment is done by a simple 4-bit subtractor. The

input of the loadable counter. This increment is done by a simple 4-bit subtractor. The ![]() output of the loadable counter is connected to the

output of the loadable counter is connected to the ![]() input and thus the counter act as mod counter. The RSH1 block is a simple 1-bit right shift block. This block has another output

input and thus the counter act as mod counter. The RSH1 block is a simple 1-bit right shift block. This block has another output ![]() which is the residual bit after shifting. The

which is the residual bit after shifting. The ![]() bit selects the negative or positive edge triggering for the dff block.

bit selects the negative or positive edge triggering for the dff block.

The above mentioned programmable clock divider can be scaled to increase the range of clock division. This can be done by increasing the width of the loadable counter and comparator.

Click here to download the code.

Thankyou SHIRSHENDU ROY for this vlog.Is it only possible to design a programmable clock divider with comparator

and counter or any other circuit is present.Can i know where should i refer for more information regarding this programmable clock divider.What will be the output waveform for the code u have given ,will it work for >50 % duty cycle.Again i kindly request u to sent refernce materials like books,vlog or research papers anything related to the basic circuit of programmable clock divider.

I have written the programmable clock divider for 50% duty cycle. Clock divider circuits for above 50% or below 50% duty cycle can be found in tutorial which published. You can use synchronous clock dividers to get programmable clock divider. You refer documents for PLL and you will automatically find the reference for programmable clock divider circuits.

Hello sir,Is it possible to design a programmable clock divider for fractional dividing factor.What modification can be done in the above circuit such that it works for odd,even and fractional dividing factor.If not possible suggest me a separate programmable clock divider that works for fractional dividing factor.For the above circuit how the testbench should be written such the way there is not glitch in the output.

Yes it can be designed…..See the post on fractional clock divider and combine these two posts.