## How to use DSD LAB IPs in a Block Design

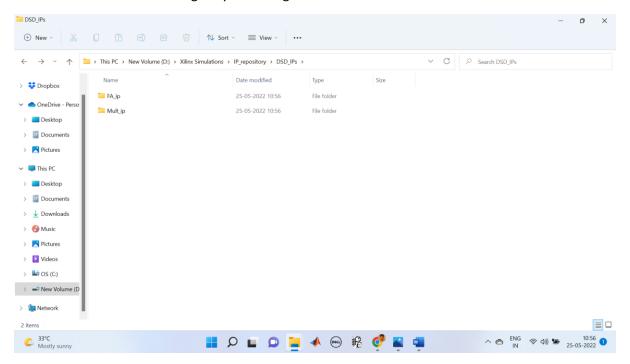

1. All the IPs from the digital system design in can be stored in a folder as shown below.

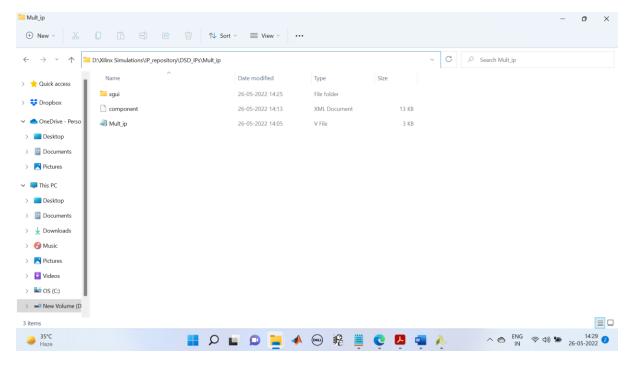

2. Here in this tutorial, the multiplier IP will be tested. This is a fixed-point rectangular multiplier whose precision and data-width can be varied. The folder contains two files, one is component files which is an .xml file responsible for the IP GUI. It also contains the encrypted Verilog source file. The xgui file contains the .tcl file of the IP.

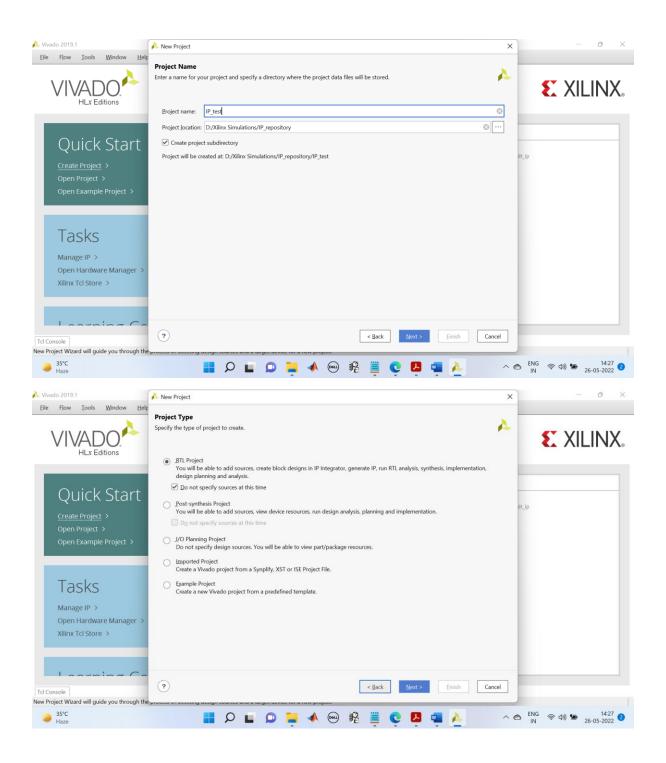

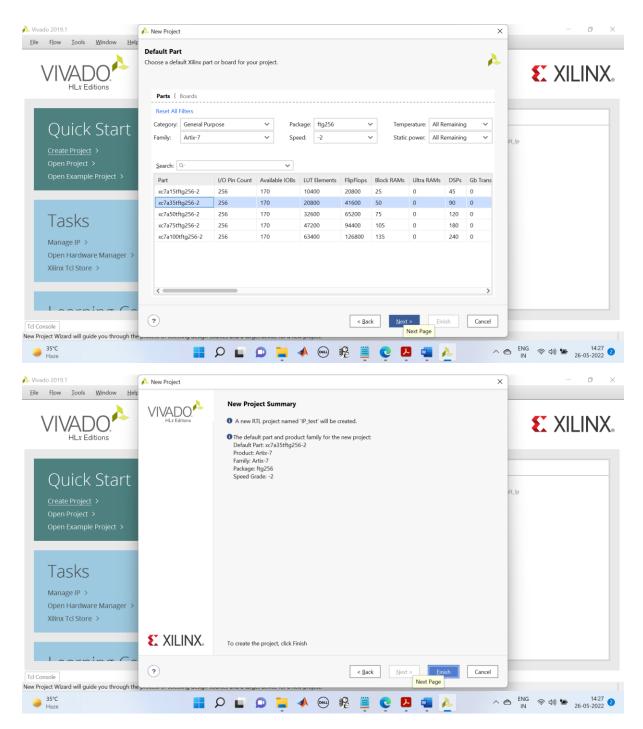

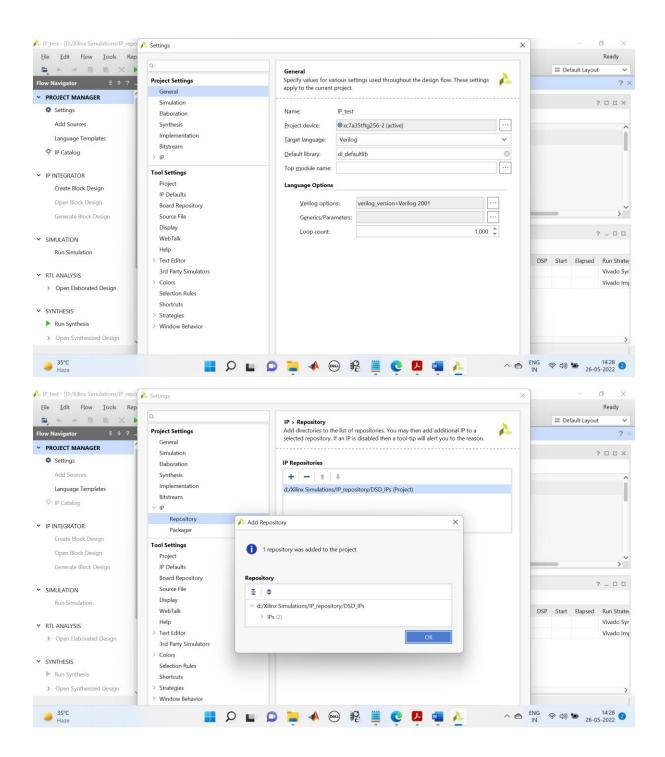

3. Open a new project where we are going to use the IP.

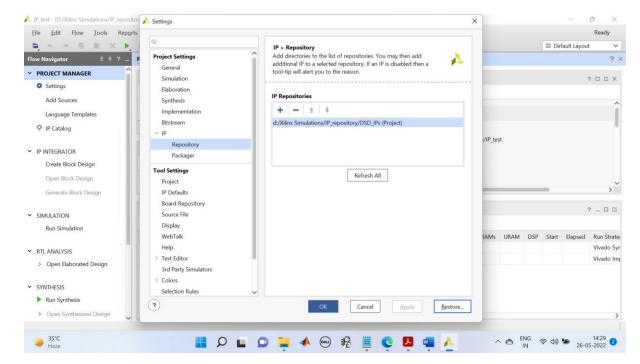

4. Go to settings and give the path of the folder where all the IPs are stored.

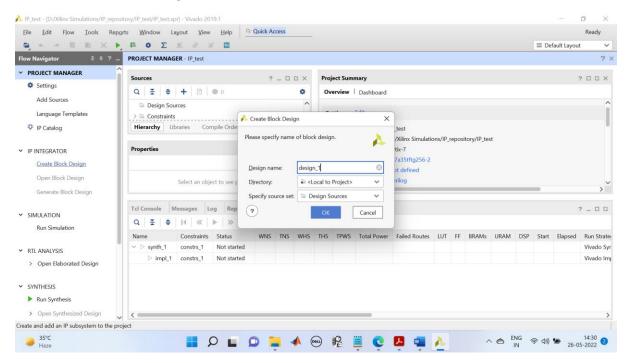

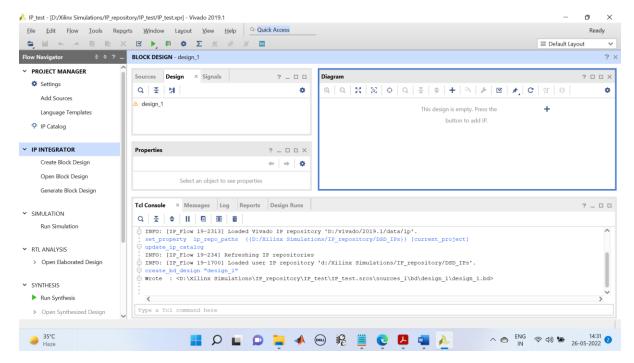

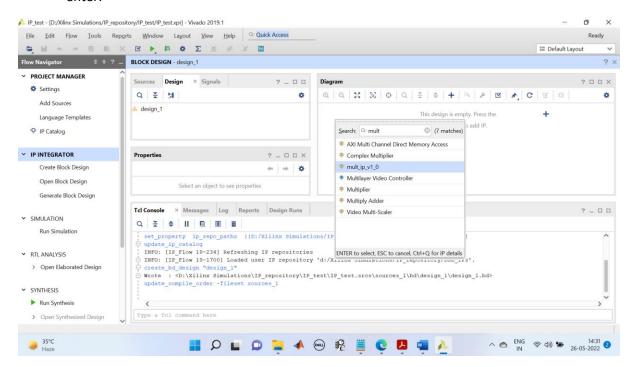

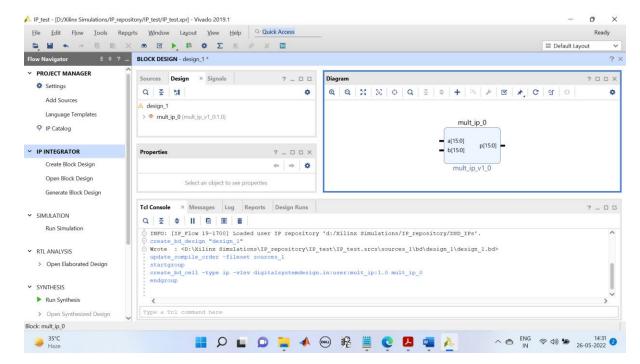

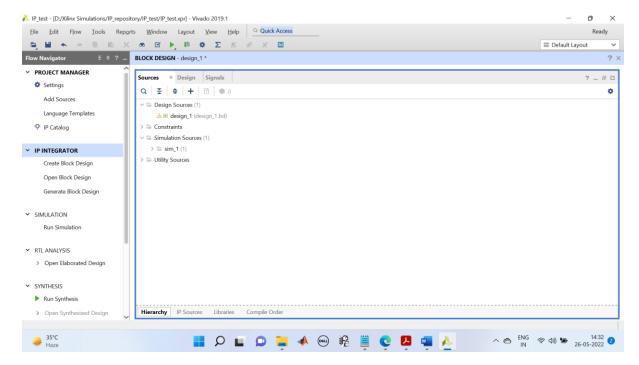

5. Create a block design where the IP will be called.

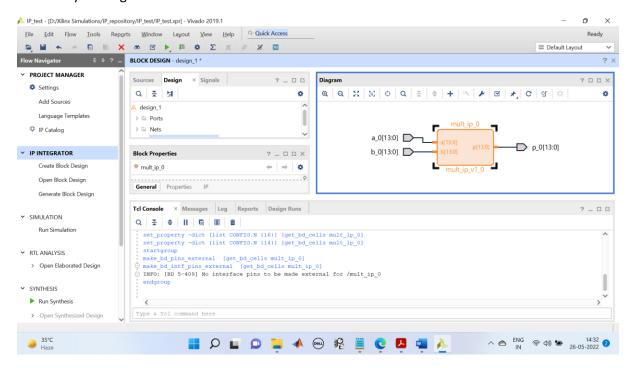

6. By clicking on the Plus symbol all type of IPs can be used. Here use the mult\_ip by pressing enter.

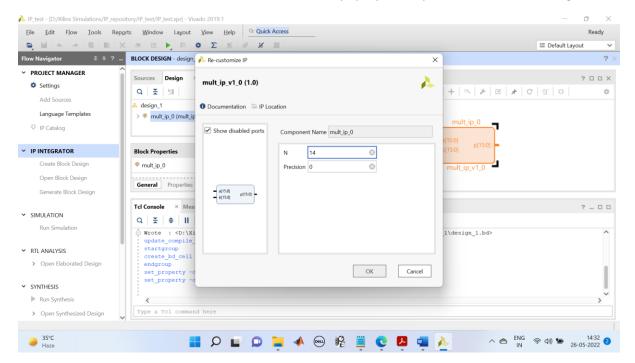

7. Double click on the IP and then a window will pop-up. Here parameters can be changed.

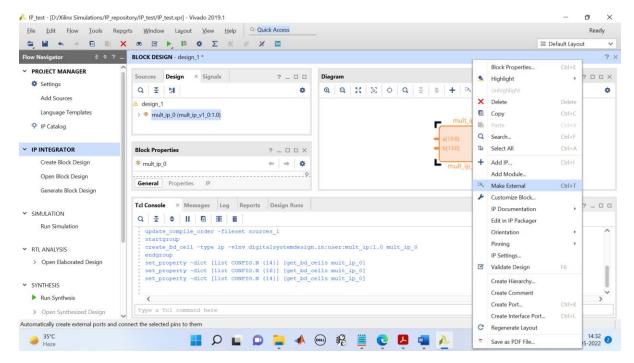

8. By clicking on the IP external connections can be done.

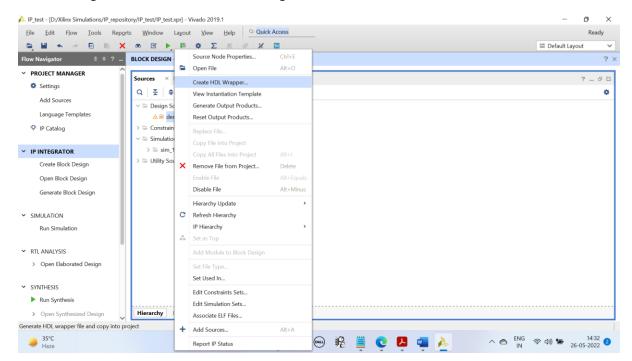

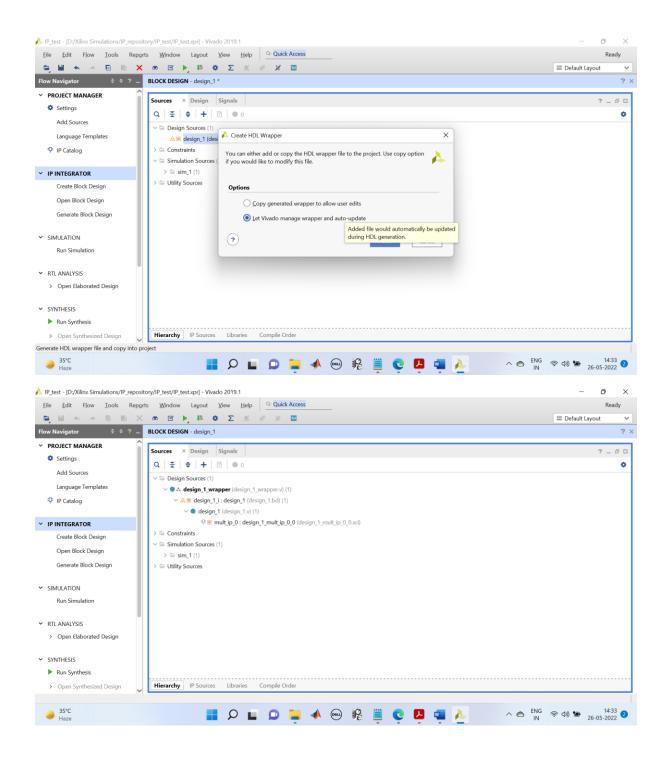

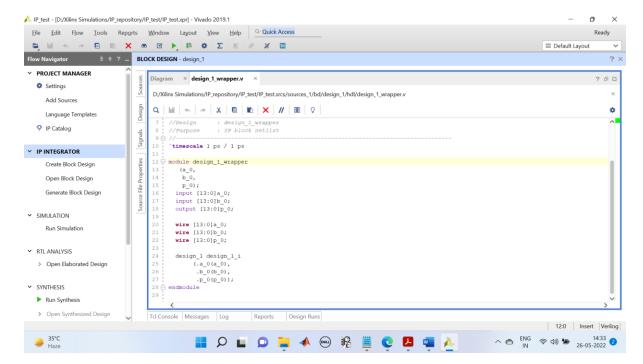

9. Create wrapper Verilog wrapper file of the block design. Without creating wrapper file block design can not be used in the Verilog files.

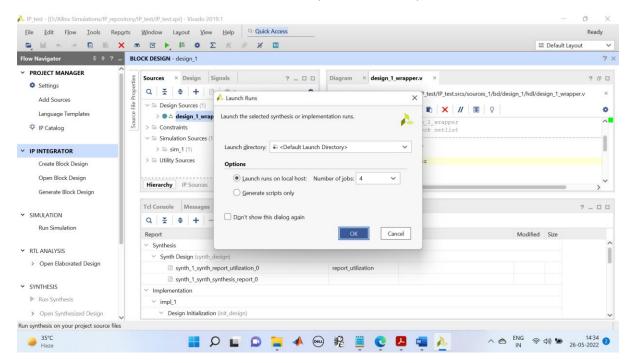

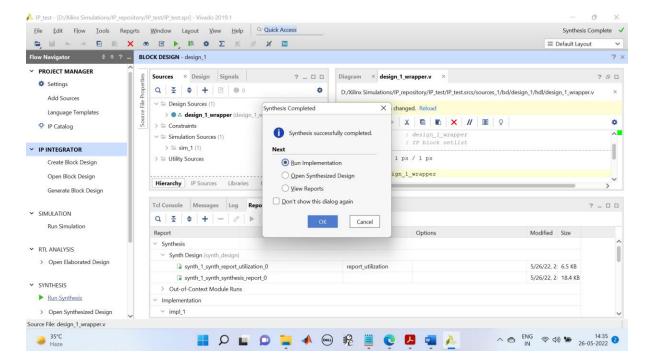

10. Our IP is now instantiated. Now it can be synthesized or Implemented.

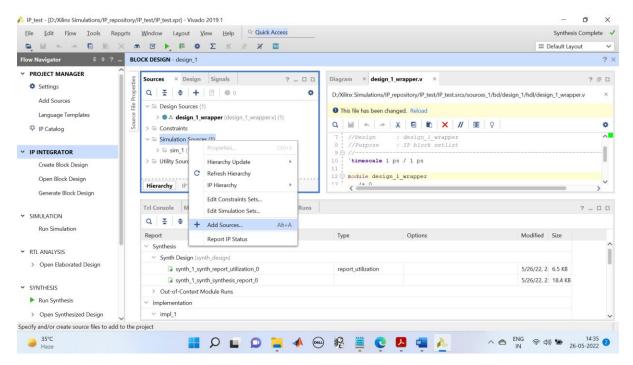

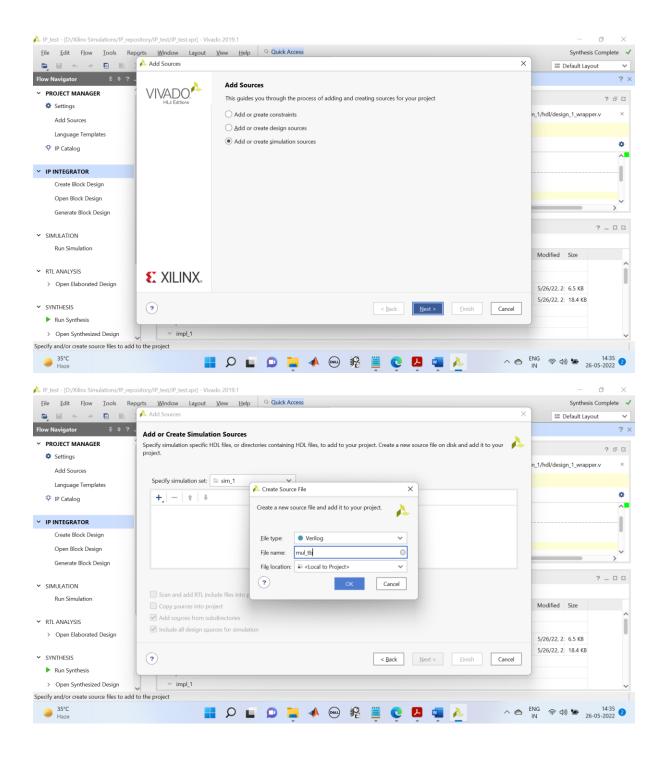

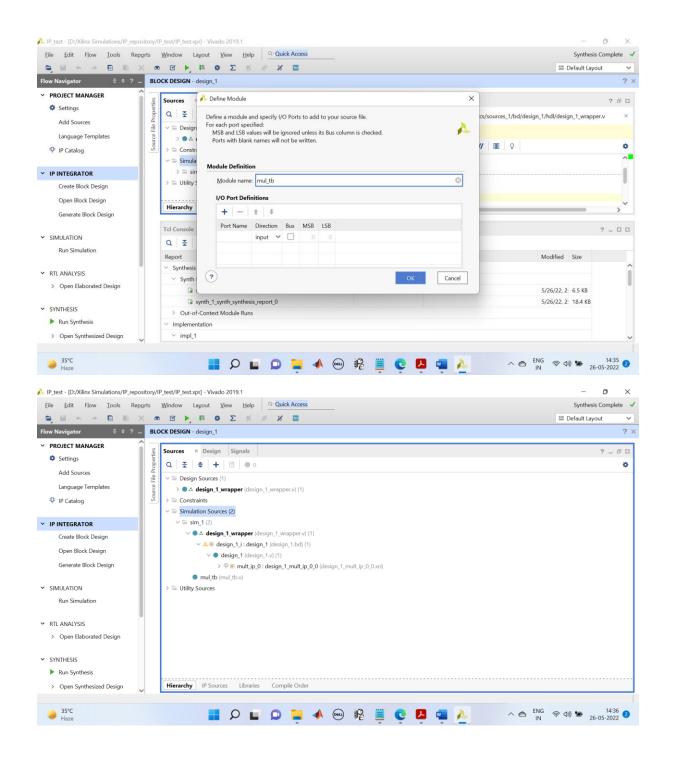

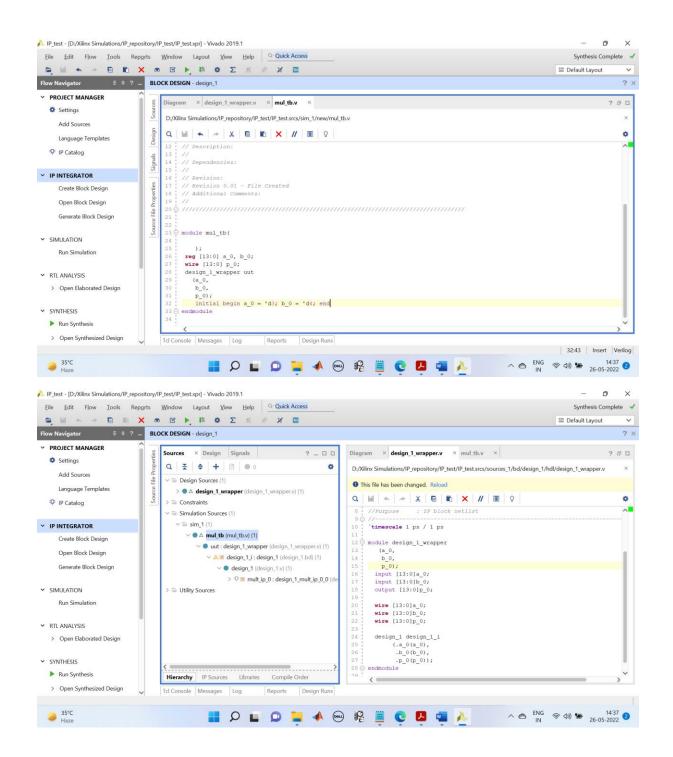

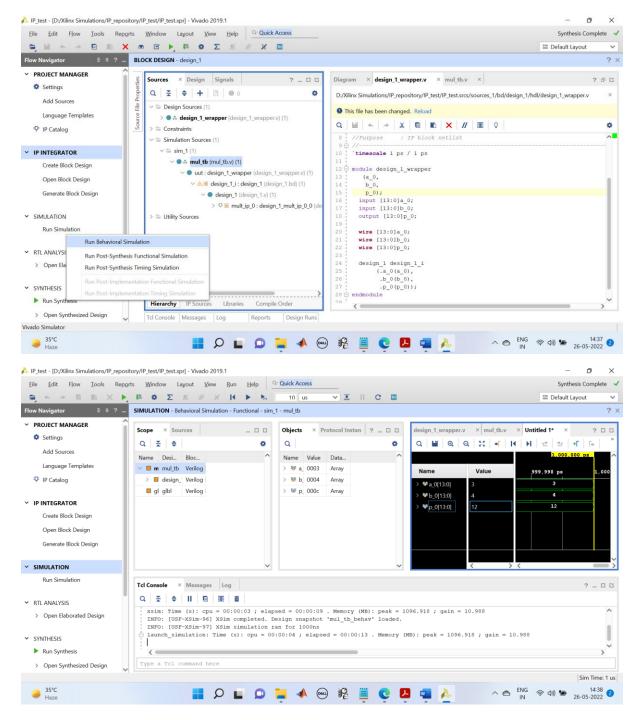

11. For simulation we need to write the test bench file.

Some times problems may arise in Simulation of the designs which uses custom IPs...

## To solve that...Few options can be tried.

- 1. Close XILINX and again open it.

- 2. Replace the IP files with originals ones

- 3. Select the Block and right click ---First click on ---Reset Output Products

Then click on Generate Output Products

- 4. In the synthesis settings, -flatten\_hierarchy---select none and apply first then again select rebuilt.

- 5. This IP is created using the XILINX Vivado tool 2019.1 and thus it may not be functionally simulated by other tools. Thus, Post Synthesis Functional simulation can be done.